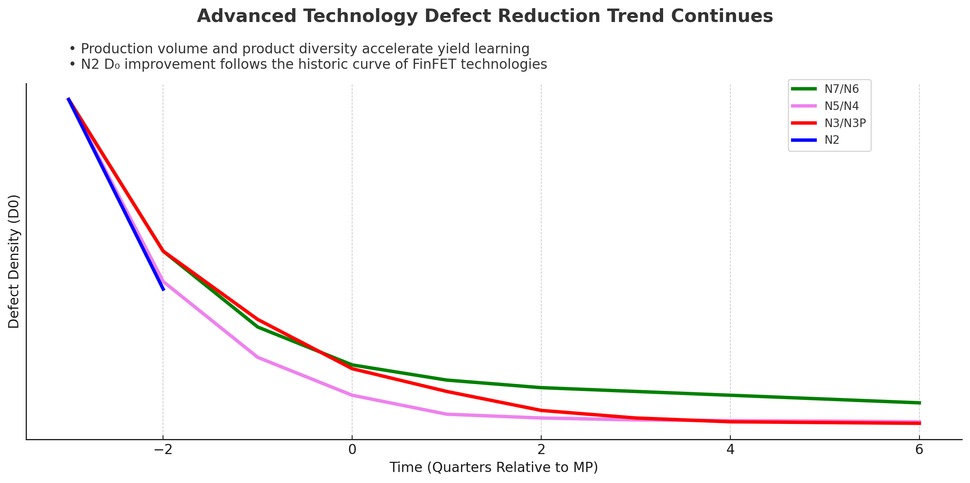

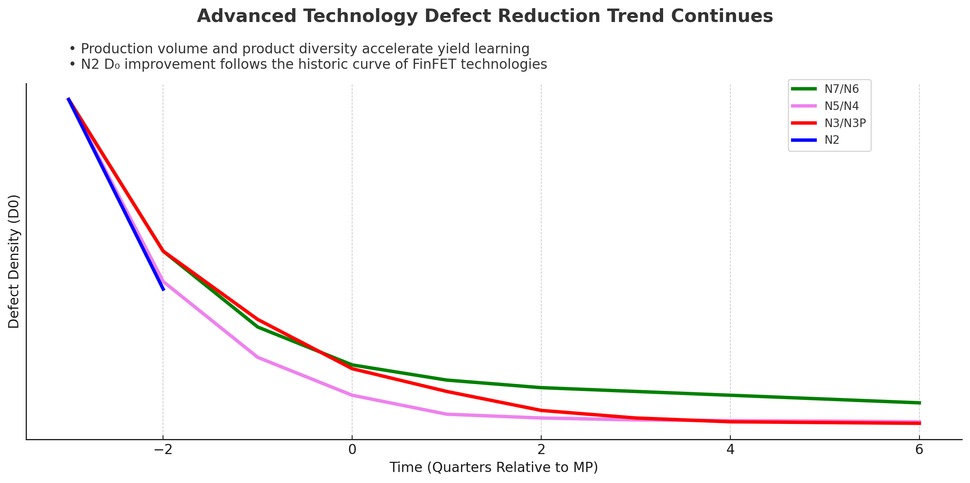

TSMC tillkännagav nyligen vid ett nordamerikansk teknikseminarium defektdensiteten (D0) för sin N2 (2NM) processteknologi jämfört med föregångarprocesserna i samma skede.Enligt företaget är defektdensiteten för N2 -processen lägre än för N3 (3Nm), N5 (5Nm) och N7 (7nm) tillverkningsnoder.Dessutom visar bilden att TSMC: s N2 -process fortfarande är två kvartal från massproduktionen, vilket innebär att TSMC förväntas börja producera 2nm -chips i slutet av det fjärde kvartalet 2025 som förväntat.

Även om TSMC: s N2 -process är företagets första processteknologi som använder Full Gate Ring (GAA) nanoskett transistorer, är defektdensiteten för denna nod lägre än föregående generationsprocess i samma skede, två kvartal före massproduktionen (MP).De tidigare generationens processer- N3/N3P, N5/N4 och N7/N6- Alla använda mogna finfälteffekttransistorer (FINFET).Även om N2 är TSMC: s första nod för att anta GAA -nanosket transistorer, är dess minskning av defektdensitet större än den tidigare generationens process innan man går in i massproduktion (HVM) milstolpe.

Detta diagram visar variationen i defektdensiteten över tid, som sträcker sig från tre kvartal före massproduktion till sex kvartal efter massproduktion.Bland alla visade noder - N7/N6 (grön), N5/N4 (lila), N3/N3P (röd) och N2 (blå) - minskar defektdensiteten avsevärt med ökande utbyte, men minskningshastigheten varierar beroende på komplexiteten hos noderna.Det är värt att notera att N5/N4 är den mest aktiva när det gäller att minska tidiga defekter, medan avkastningsförbättringen av N7/N6 är relativt mild.Den initiala defektnivån för N2 -kurvan är högre än för N5/N4, men minskar sedan kraftigt, vilket är mycket nära defektreduktionsbanan för N3/N3P.

Sliden betonar att utbytet och produktdiversiteten förblir viktiga drivfaktorer för att påskynda defektdensitetsförbättringen.Större produktion och diversifierade produkter med samma process kan identifiera och korrigera defektdensitet och ge problem snabbare, vilket gör det möjligt för TSMC att optimera defekt inlärningscykler.TSMC uppgav att dess N2-tillverkningsteknologi har erhållit fler nya chips än sin föregångare teknik (eftersom TSMC nu producerar N2-chips för smartphone och högpresterande datorkunder (HPC) -kunder i riskzonen), och defektdensitetsnedgången bekräftar i princip detta.

Med tanke på de riskfaktorer som åstadkommits genom införandet av en ny transistorarkitektur är det särskilt viktigt för defektreduktionshastigheten för N2 att förbli konsekvent med tidigare FINFET -baserade noder.Detta indikerar att TSMC framgångsrikt har överfört sin processinlärnings- och felhanteringskompetens till den nya GAAFET -eran utan att möta betydande bakslag.

RFQs/beställning (0)

RFQs/beställning (0)

RFQs/beställning (0)

RFQs/beställning (0)