## LTC5598

# DESCRIPTION

Demonstration circuit 1455A is a high linearity direct quadrature modulator featuring the LTC5598.

The LTC<sup>®</sup>5598 is a direct I/Q modulator designed for high performance wireless applications, including wireless infrastructure. It allows direct modulation of an RF signal using differential baseband I and Q signals. It supports point-to-point microwave link, GSM, EDGE, CDMA, 700MHz band LTE, CDMA2000, CATV applications and other systems. It may also be configured as an image reject upconverting mixer, by applying 90° phase-shifted signals to the I and Q inputs.

The LTC5598's I/Q baseband inputs consist of voltageto-current converters that in turn drive double-balanced mixers. The outputs of these mixers are summed and applied to a buffer, which converts the differential mixer signals to a 50 $\Omega$  single-ended buffered RF output. The four balanced I and Q baseband input ports are intended for DC coupling from a source with a commonmode voltage level of about 0.5V. The LO path consists of an LO buffer with single-ended or differential inputs, and precision quadrature generators that produce the LO drive for the mixers. The supply voltage range is 4.5V to 5.25V, with about 165mA current.

Demonstration circuit 1455A is designed for evaluating the LTC5598 IC at frequencies from 80MHz to 1300MHz. With a few component changes, it can be easily optimized for evaluations at lower or higher frequencies. Refer to "Application Note" section and the LTC5598 data sheet for details.

Design files for this circuit board are available. Call the LTC factory.

#### Table 1. Typical Demo Circuit Performance Summary

$T_A = 25^{\circ}C$ ;  $V_{CC} = 5V$ , EN = 5V; BBPI, BBMI, BBPQ, BBMQ common-mode DC Voltage  $V_{CMBB} = 0.5V_{DC}$ , single-tone I and Q baseband input signal = 100kHz CW,  $0.8V_{PP,DIFF}$ , two-tone I and Q baseband input signal = 2MHz and 2.1MHz CW,  $0.5V_{PP,DIFF}$  each tone, I and Q 90° shifted (lower side-band selection);  $P_{LO} = 0dBm$ , single-ended;  $f_{RF} = f_{LO} - f_{BB}$ , unless otherwise noted.

| PARAMETER                              | CONDITIONS                                                            | TYPICAL PERFO            | TYPICAL PERFORMANCE      |                          |  |

|----------------------------------------|-----------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|--|

| Supply Voltage                         |                                                                       | 4.5V to 5.25V            | 4.5V to 5.25V            |                          |  |

| Supply Current                         | I <sub>CC1</sub> +I <sub>CC2</sub> , EN = High                        | 165mA                    |                          |                          |  |

| Sleep Current                          | I <sub>CC1</sub> +I <sub>CC2</sub> , EN = Low                         | 240µA                    |                          |                          |  |

| Baseband Bandwidth                     | -3dB Bandwidth                                                        | > 400MHz                 |                          |                          |  |

| Baseband Input Current                 | Single-Ended                                                          | -68µA                    |                          |                          |  |

| Baseband Input Resistance              | Single-Ended                                                          | -7.4kΩ                   | -7.4kΩ                   |                          |  |

| Baseband DC Common-Mode Voltage        | Externally Applied                                                    | 0.5V                     |                          |                          |  |

| Baseband Amplitude Swing               | No Hard Clipping, Single-Ended                                        | 0.86V <sub>PP</sub>      |                          |                          |  |

| LO Input Frequency Range               | Standard Demo Board, S <sub>11, ON</sub> < -10dB                      | 80MHz to 1300MHz         |                          |                          |  |

| LO Input Power Range, Differential     |                                                                       | -10 to 20dBm             |                          |                          |  |

| LO Input Power Range, Single-Ended     |                                                                       | -10 to 12dBm             |                          |                          |  |

| F Output Frequency Range               |                                                                       | 5 to 1600MHz             |                          |                          |  |

|                                        |                                                                       | f <sub>LO</sub> = 140MHz | f <sub>LO</sub> = 450MHz | f <sub>L0</sub> = 900MHz |  |

| Conversion Voltage Gain                | 20 • Log (V <sub>RF, OUT, 50Ω</sub> / V <sub>IN, DIFF, I OR Q</sub> ) | -2dB                     | -2.1dB                   | -2dB                     |  |

| Absolute Output Power                  | 1VPP, DIFF on each I and Q Inputs                                     | 2dBm                     | 1.9dBm                   | 2dBm                     |  |

| Output 1dB Compression                 |                                                                       | 8.5dBm                   | 8.4dBm                   | 8.5dBm                   |  |

| Output 2nd Order Intercept             | IM2 is Measured at LO – 4.1MHz                                        | 74dBm                    | 72dBm                    | 69dBm                    |  |

| Output 3 <sup>rd</sup> Order Intercept | IM3 is Measured at LO – 1.9MHz and LO – 2.2MHz                        | 27.7dBm                  | 25.5dBm                  | 22.9dBm                  |  |

| RF Output Noise Floor                  | No Baseband AC Input Signal (6MHz offset)                             | -161.2dBm/Hz             | -160.9dBm/Hz             | -160.3dBm/Hz             |  |

| Image Rejection                        | Without Image Nulling                                                 | -50.4dBc                 | -55dBc                   | -54dBc                   |  |

| LO Feedthrough                         | Without LO Feedthrough Nulling                                        | -55dBm                   | -51dBm                   | -48dBm                   |  |

# **APPLICATION NOTE**

#### **ABSOLUTE MAXIMUM RATINGS**

**NOTE:** Stresses beyond Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

| Supply Voltage5.6V                      |  |  |  |  |

|-----------------------------------------|--|--|--|--|

| Common Mode Level of BBPI, BBMI and     |  |  |  |  |

| BBPQ, BBMQ0.6V                          |  |  |  |  |

| LOP, LOM Input20dBm                     |  |  |  |  |

| Voltage on Any Pin                      |  |  |  |  |

| Not to Exceed0.3V to $V_{CC}$ + 0.3V    |  |  |  |  |

| T <sub>JMAX</sub> 150°C                 |  |  |  |  |

| Operating Temperature Range40°C to 85°C |  |  |  |  |

| Storage Temperature Range65°C to 150°C  |  |  |  |  |

### **POWER SUPPLY CONSIDERATION**

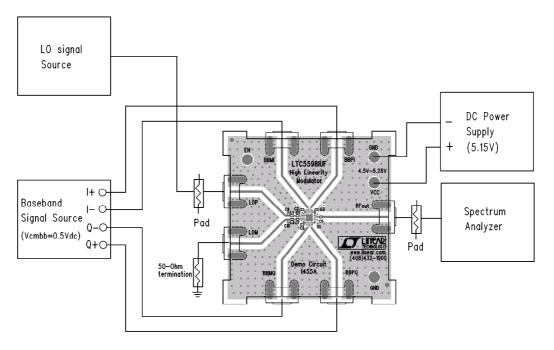

In demonstration circuit 1455A (see Figure 3 for schematic), resistors R1 and R2 reduce the charging current in the power supply bypass capacitors C1 and C4 and reduce supply ringing during a fast power ramp-up in case an inductive cable is connected to the  $V_{CC}$  and GND. While the LTC5598 IC is enabled, the voltage drop across R1 and R2 is approximately 0.15V. If the power supply used ramps up slower than 10V/µs and limits its output overshoot to below 5.6V, R1 and R2 can be omitted.

#### **ENABLE INTERFACE**

The EN input in demonstration circuit 1455A controls the operation of the LTC5598 IC. When a voltage of 2V or higher is applied, the IC is turned on. When the input voltage falls below 1V, the IC is turned off and enters sleep mode. If the EN input is not connected, the LTC5598's 125k $\Omega$  on-chip pull-up resistor assures the IC is enabled. The voltage applied to the EN input must never exceed V<sub>CC</sub> by more than 0.3V. Surpassing this limit may cause permanent damage to the IC.

#### **BASEBAND INPUT INTERFACE**

Demonstration circuit 1455A has two channels of high impedance differential inputs to which external I and Q

Because the LTC5598 baseband inputs' single-ended impedance is -7.4k each, it is important to keep the source resistance low enough such that the parallel value remains positive for the entire baseband frequency range from DC to 500MHz.

A common-mode voltage of 0.5V (maximum 0.6V) must be externally applied to the baseband inputs for proper operation. In any case, the baseband inputs must NOT be left floating to avoid damages to the LTC5598 IC.

### LO INPUT INTERFACE

The standard demonstration circuit 1455A can accept either single-ended or differential LO inputs. If singleended LO input is used, the LO signal should be applied to the LOP port, and the LOM port should be terminated in 50 $\Omega$ . In most cases, single-ended LO drive should be sufficient. However, differential LO drive can improve large-signal output noise floor by several dB.

Demonstration circuit 1455A's LO inputs are optimized for maximum bandwidth, with better than 10dB input return loss from 80MHz to 1300MHz. Impedance matching for the low-end and the high-end of the operating frequency range can be improved using different LO matching component values, as shown in Table 2. Refer to the LTC5598 datasheet for more information and impedance data.

| •                           | • •    |         |        |

|-----------------------------|--------|---------|--------|

| LO Input<br>Frequency Range | C5, C7 | C9, C10 | L1, L2 |

| 80 to 1300MHz*              | 10nF*  | 2.2pF*  | 3.3nH* |

| <5 to 250MHz                | 100nF  | 120Ω    | 0Ω     |

| 1150 to >1600MHz            | 10nF   | 2.7pF   | 1.5nH  |

\*Standard demonstration circuit 1455A configuration.

### **RF OUTPUT INTERFACE**

The LTC5598's RF output is single-ended and is internally matched to  $50\Omega$  for the entire operating frequency range. No external matching is needed. A 10nF series

# TEST EQUIPMENT AND SETUP

The LTC5598 is a high linearity direct quadrature modulator IC with very high output 2nd and 3rd order intercepts. Accuracy of its performance measurement is highly dependent on equipment setup and measurement technique. Then following precautions are recommended:

- 1. Use high performance signal generators with low harmonic output. Otherwise, utilize filters at the signal generator outputs to suppress higher-order harmonics. The third LO harmonic should be lower than -60dBc to maintain best image suppression.

- 2. Cables connecting the baseband signal source to the demonstration circuit baseband inputs should provide a well-defined match for the entire baseband frequency range up to 500MHz. Therefore, high quality coaxial cables are recommended.

- If possible, use small attenuator pads with good VSWR on the demonstration circuit LO input and RF output ports to improve source and load match to reduce reflections, which may degrade measurement accuracy.

# **QUICK START PROCEDURE**

Demonstration circuit 1455A is easy to set up to evaluate the performance of the LTC5598. Refer to Figure 1 and Figure 2 for proper measurement equipment connections and follow the procedure below:

**NOTE:** Care should be taken to never exceed absolute maximum input ratings. Observe standard ESD precautions and avoid static discharge.

#### **TURNING ON THE DEMONSTRATION CIRCUIT**

**1.** Remove the demonstration circuit from its protective packaging in an ESD-safe working area.

capacitor is installed at the RF output of the demonstration circuit to provide DC isolation to the external load.

- 4. Use narrow resolution bandwidth (RBW) and engage video averaging on the spectrum analyzer to lower the displayed average noise level (DANL) in order to improve sensitivity and to increase dynamic range. However, the trade off is increased sweep time.

- 5. Spectrum analyzers can produce significant internal distortion products if they are overdriven. Generally, spectrum analyzers are designed to operate at their best with about -30dBm to -40dBm at their input filter or preselector. Sufficient spectrum analyzer input attenuation should be used to avoid saturating the instrument, but too much attenuation reduces sensitivity and dynamic range.

- 6. Before taking measurements, the system performance should be evaluated to ensure that: 1) clean input signal can be produce, 2) the third LO harmonic is below -60dBc, 3) the spectrum analyzer's internal distortion is minimized, 4) the spectrum analyzer has enough dynamic range and sensitivity, and 5) the system is accurately calibrated for power and frequency.

- 2. Turn off DC power supply. Turn off baseband and LO signal sources outputs.

- **3.** With the power supply and the signal sources turned off, connect the four baseband inputs: BBPI, BBMI, BBPQ, and BBMQ.

- 4. Turn on baseband signal source DC bias, and slowly increase the DC common-mode voltage ( $V_{CMBB}$ ) to 0.5V. Do not exceed 0.6V.

- 5. Connect DC power supply, and slowly increase  $\rm V_{CC}$  to 5.15V. Using a voltmeter, verify the supply voltage

at the LTC5598  $V_{CC}$  pins 18 and 24 is 5V. Adjust if necessary. Do not exceed 5.6V at pins 18 and 24.

- **6.** Verify the total  $V_{CC}$  supply current is approximately 165mA. The demonstration circuit is now turned on and is ready for measurements.

- 7. The turn off procedure is the reverse of the turn on procedure. Make sure  $V_{CC}$  is removed before  $V_{CMBB}$ .

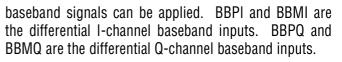

#### **RETURN LOSS MEASUREMENTS (FIGURE 1)**

- **1.** Turn on the demonstration circuit by following the procedure above.

- 2. Configure the Network Analyzer for return loss measurement, set appropriate frequency range, and set the test signal to 0dBm.

- 3. Calibrate the Network Analyzer.

- 4. Connect a 50  $\Omega$  termination to the LOM input.

- 5. Connect the Network Analyzer test-set cable to the LOP input, and measure single-ended LO input return loss.

- **6.** Connect the Network Analyzer test-set cable to the RF output, and measure RF output return loss.

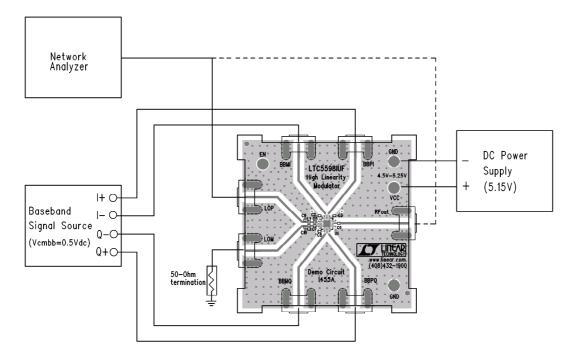

#### VOLTAGE CONVERSION GAIN, OUTPUT 1dB COMPRESSION, IMAGE REJECTION, AND LO FEEDTHROUGH MEASUREMENTS (FIGURE 2)

- **1.** Turn on the demonstration circuit by following the procedure above.

- 2. Connect the RF output to the Spectrum Analyzer.

- **3.** Connect a 50 $\Omega$  termination to the LOM input.

- **4.** Connect the LO source to LOP input and apply a 140MHz, 0dBm, CW signal.

- 5. Set the baseband signal source to provide a 100kHz,  $0.8V_{PP, DIFF}$  baseband input signal. The l-and the Q-channels should be 90° shifted for lower side-band selection.

- **6.** Measure the modulator RF output on the Spectrum Analyzer at 139.9MHz.

- 7. Calculate Conversion Voltage Gain:

$G_V = 20 \bullet Log \ (V_{RF, \ OUT, \ 50\Omega} \ / \ V_{IN, \ DIFF, \ I \ OR \ Q})$

- 8. Measure Output 1dB Compression point by increasing input signal level until the Conversion Voltage Gain degrades by 1dB.

- 9. Measure Image Rejection at 140.1MHz.

- **10**. Measure LO Feedthrough at 140MHz.

#### OUTPUT 2ND ORDER AND 3RD ORDER INTERCEPT MEASUREMENTS (FIGURE 2)

- 1. Set the baseband signal source to provide a twotone baseband input signal at 2MHz and 2.1MHz with  $0.5V_{PP, DIFF}$  each tone. The I- and the Qchannels should be 90° shifted for lower sideband selection.

- 2. Measure the modulator RF output on the Spectrum Analyzer:

- a. The two-tone RF output signals are located at 137.9 MHz and 138MHz.

- b. The 2nd order intermodulation product is located at 135.9MHz.

- c. The 3rd order intermodulation products are located at 137.8MHz and 138.1MHz.

- 3. Calculate the Output 2nd and 3rd Order Intercepts:

$OIP2 = 2 \bullet P_{OUT} - P_{IM2}$

$OIP3 = (3 \bullet P_{OUT} - P_{IM3}) / 2$

Where  $P_{OUT}$  is the lowest power level of the two RF output signals at either 137.9MHz or 138MHz,  $P_{IM2}$  is the 2nd order intermodulation product level at 135.9MHz, and  $P_{IM3}$  is the largest 3rd order intermodulation product level at either 137.8MHz or 138.1MHz. All units are in dBm.

Alternatively, the output intercept can be calculated using the power difference between the desired output signal and the intermodulation products:

$OIP2 = \Delta_{IM2} + P_{OUT}$

$\mathsf{OIP3} = (\Delta_\mathsf{IM3})/2 + \mathsf{P}_\mathsf{OUT}$

Where  $\Delta_{IM(2 \text{ OR } 3)} = P_{OUT} - P_{IM(2 \text{ OR } 3)}$ .

Figure 1. Proper Equipment Setup for Return Loss Measurements

Figure 2. Proper Equipment Setup for RF Performance Measurements

**LINEAR** TECHNOLOGY

1