# 5A Single Cell Li-Ion Switching Battery Charger with Power Path Management and USB-OTG Boost Mode

### **General Description**

The RT9466 is a switch-mode single cell Li-lon/Li-Polymer battery charger for portable applications. It integrates a synchronous PWM controller, power MOSFETs, input current sensing and regulation, high-accuracy voltage regulation, and charge termination. The charge current is regulated through integrated sensing resistors. The RT9466 also features USB On-The-Go (OTG) support.

The RT9466 optimizes for charging task by using a control algorithm to vary the charge rate for different modes, including pre-charge mode, fast charge mode (constant voltage and constant current). The key charge parameters are programmable through an I<sup>2</sup>C interface. The RT9466 will resume the charge cycle whenever the battery voltage falls below an internal recharge threshold, and can automatically enter sleep mode if the input power supply is removed.

Other features include under-voltage protection, over voltage protection, thermal regulation and reverse leakage protection.

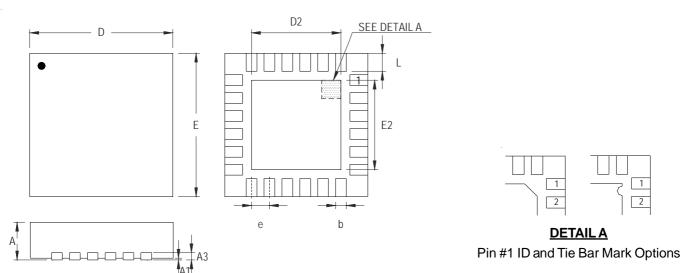

The RT9466 is available in a WQFN-24L 4x4 package.

### **Applications**

- Cellular Telephones

- Personal Information Appliances

- Tablet PC, Power Bank

- Portable Instruments

### **Ordering Information**

Package Type

QW: WQFN-24L 4x4 (W-Type)

(Exposed Pad-Option 2)

Lead Plating System

G: Green (Halogen Free and Pb Free)

#### Richtek products are:

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

### **Features**

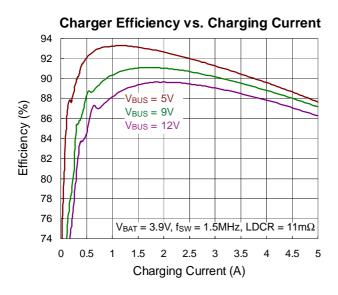

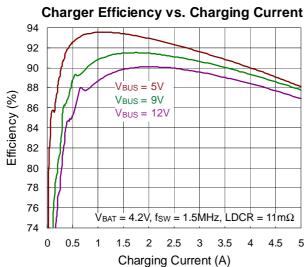

- High Efficiency 5A, 1.5MHz Switching Charger with Output Inductor DFE252012F, TOKO

- ▶ Charging Efficiency 90.25% at ICHG = 2A

- ▶ Charging Efficiency 88.86% at ICHG = 3A

- ▶ Charging Efficiency 84.2% at ICHG = 5A

- Synchronous 1.5MHz/0.75MHz Fixed-Frequency PWM Controller with Up to 95% Duty Cycle

- Power Path Management by BATFET Control

- Support High Voltage Input (9V/12V)

- Support High Voltage Input Adapter (Pump Express 1.0/2.0)

- Support IR Compensation Function from Charger Output to Cell Terminal

- Optimize Input Sourcing Capability to Prevent Overload

- ▶ AICR Current Limit Setting via I<sup>2</sup>C

- **▶ ILIM Pin for Current Limit Setting**

- ▶ Average Input Current Limit Measurement

- Shipping Mode for Battery Leakage Reduction

- ▶ Wake Up System, Exit Shipping Mode, and Reset System by QON Pin

- Automatic Charging

- Average Input Current Regulation (AICR):

0.1A to 3.25A in 50mA Steps

- Charge Current Regulation Accuracy: ±7%

- Charge Voltage Regulation Accuracy : ± 1% (0 to 85°C)

- Protection for Overall System Considerations

- ▶ Thermal Regulation for Current Reduction and Over-Temperature Protection

- Input Over-Voltage Protection

- Input Bad Adapter Protection

- Battery Over-Voltage Protection

- Support ADC Conversion for

- ▶ VBUS, VBAT, VSYS, REGN, TS\_BAT, IBUS, IBAT, TEMP\_JC

- INT Output for Communication with Host Through I<sup>2</sup>C (Watch Dog/Polling Function)

## **Marking Information**

4S=YM DNN 4S=: Product Code YMDNN: Date Code

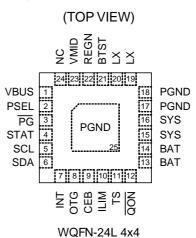

## **Pin Configuration**

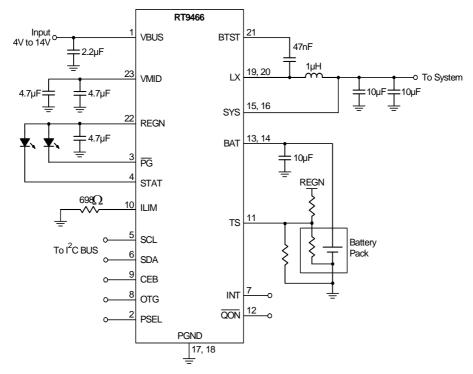

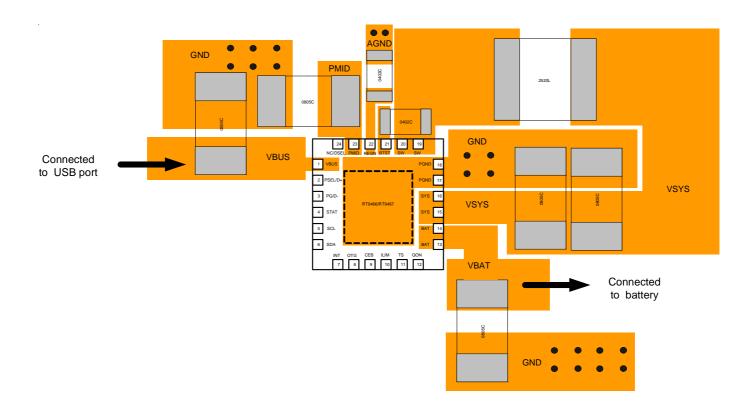

# **Typical Application Circuit**

#### Below are recommended components information

| Pin  | Description    | Part Number       | Package   | Manufacturer |

|------|----------------|-------------------|-----------|--------------|

| VBUS | 2.2μF/25V/X5R  | GRM155R61E225KE11 | 0402      | muRata       |

| VMID | 4.7μF/25V/X5R  | GRM188R61E475KE11 | 0603      | muRata       |

| BTST | 47nF/16V/X5R   | GRM033R61C473KE84 | 0201      | muRata       |

| SYS  | 10μF/6.3V/X5R  | GRM185R60J106ME15 | 0603      | muRata       |

| BAT  | 10μF/6.3V/X5R  | GRM185R60J106ME15 | 0603      | muRata       |

| REGN | 4.7μF/6.3V/X5R | GRM155R60J475ME47 | 0402      | muRata       |

| LX   | 1μH/20%        | DFE252012F-1R0    | 2.5 x 2mm | TOKO         |

| ILIM | 698Ω/1%        | RR0306S-6980-FNH  | 0201      | CYNTEC       |

# **Functional Pin Description**

| Pin No. | Pin Name | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VBUS     | Power input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2       | PSEL     | Power source selection input : High : USB host, $I_{BUS} = 500 \text{mA}$ ; Low : adapter source, $I_{BUS} = 3.25 \text{A}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3       | PG       | Open-drain output. Low if the VBUS voltage is between V <sub>UVLO</sub> and V <sub>BUS_OVP</sub> ; VBUS is higher than VBAT. VBUS current capability is larger than 50mA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4       | STAT     | Charge status indication, open-drain output that indicates charge is in progress when held low and charge is finished when held High. If any fault occurs, CHG_STAT will blink at the frequency of 1Hz. Connect a $2.2k-10k\Omega$ pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5       | SCL      | $\ensuremath{\text{I}^2\text{C}}$ interface serial clock input. Open-drain. An external pull-up resistor is required                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6       | SDA      | I <sup>2</sup> C interface serial data input/output. Open-drain. An external pull-up resistor is required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

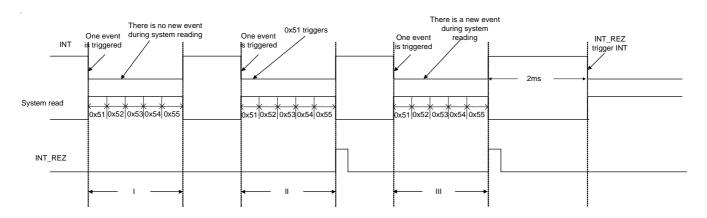

| 7       | INT      | Interrupt output, active-low open-drain. Indicator of the charger/Boost event for system processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 8       | ОТС      | OTG boost mode enable control, active-high. Act with OTG_PIN_EN (Addr0x01[1]).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9       | CEB      | Charger enable input, active-low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 10      | ILIM     | Input current limit setting pin. A resistor is connected from ILIM pin to ground to set the maximum input current limit. The actual input current limit is the lower value set through the ILIM pin and IAICR register bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

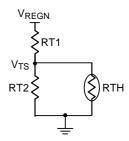

| 11      | TS       | Battery temperature-sense input, connected to a resistor divider for temperature programming. If there is no need for the battery temperature-sense function, a $50k\Omega$ resistor is connected to REGN and another $50k\Omega$ resistor to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12      | QON      | Internal BATFET enable control input. In shipping mode, $\overline{\text{QON}}$ is pulled Low for the duration of tshipmode (typical 0.9s) to exit shipping mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 13, 14  | BAT      | Charge current output node for battery connection. The internal BATFET is connected between VSYS and BAT. Connect a $10\mu F$ ceramic capacitor between BAT and ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 15, 16  | SYS      | System connection node. The internal BATFET is connected between SYS and BAT. Connect a $20\mu F$ ceramic capacitor between SYS and ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 17, 18  | PGND     | Power ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 19, 20  | LX       | Switch node for output inductor connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 21      | BTST     | Bootstrap capacitor connection for High-Side Gate Driver. Connect a capacitor from BTST to LX to power the internal gate driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 22      | REGN     | <ul> <li>Regulated output voltage to supply for the PWM low-side gate driver and the bootstrap capacitor. Connect a 4.7μF ceramic capacitor from REGN to GND.</li> <li>1. If VBUS is plugged in, REGN will be powered by VBUS and regulated to 4.9V.</li> <li>2. If VBUS is unplugged, the charger will operate in sleep mode and the REGN voltage will be 0V.</li> <li>* For #2. : Since the REGN voltage is also used to power the TS resistor, when the charger is in sleep mode, the REGN will be woken up (be reactivated) if VBAT is greater than forward voltage (VF) of the internal high-side (HS) MOS diode by V<sub>SLEEP_EXIT</sub> with all function of the internal ADC being activated and I<sup>2</sup>C R/W. The REGN wake-up time is 500ms.</li> </ul> |

Copyright@2017 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

| Pin No.          | Pin Name | Pin Description                                                                                                                    |

|------------------|----------|------------------------------------------------------------------------------------------------------------------------------------|

| 23               | VMID     | Connection point between the reverse blocking MOSFET and the high-side switching MOSFET.                                           |

| 24               | NC       | No connection.                                                                                                                     |

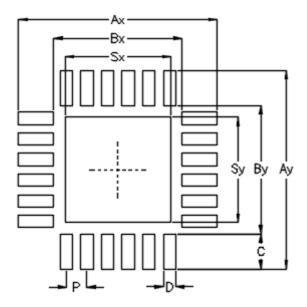

| 25 (Exposed Pad) | PGND     | Power ground. The exposed pad must be connected to GND and well soldered to a large PCB copper area for maximum power dissipation. |

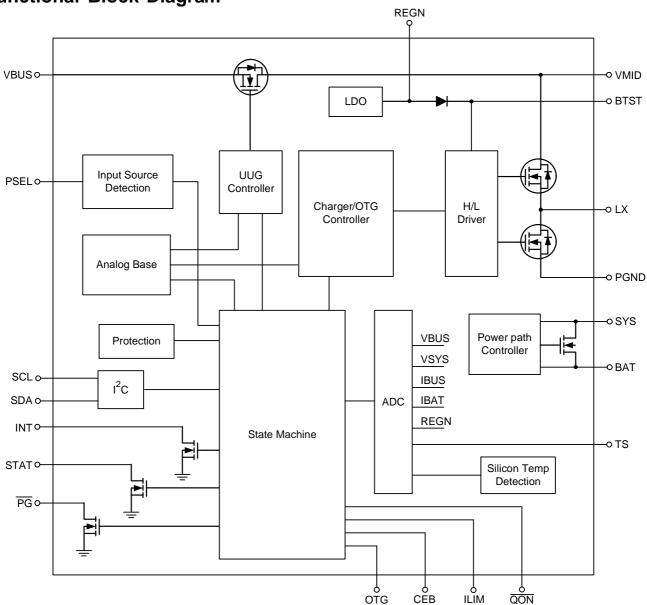

### **Functional Block Diagram**

### **Operation**

The RT9466 is an integrated single cell Li-ion battery switching charger with power path controller.

#### **Base Circuits**

Base circuits provide the internal power, VREGN and reference voltage and bias current.

#### **Protection Circuits**

The protection circuits include the VINOVP, VINUVLO, BATOVP and OTP circuits. The protection circuits turn off the charging when the input power or die temperature is in abnormal level.

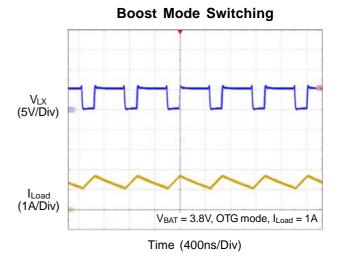

#### **Buck Regulator for Charging and Boost Regulator**

#### as OTG

The multi-loop controller controls the operation of charging process and current supply to the system. It also controls the circuits as a Boost converter for OTG applications.

#### **Battery Detection**

The RT9466 is capable of doing the battery absence detection. The detection protects the charger when battery is removed accidentally.

#### **Adapter Detection**

If the poor input power source is connected to the RT9466, the operation will be shut down by the adapter detection.

#### **Power Path Management and Control**

Once the battery voltage increases to a defined system minimum regulation voltage, the internal path between SYS and BAT will be fully turned on. That is, a better charging efficiency can be achieved. When end of charge occurs, the charging will stop and the internal path will be turned off.

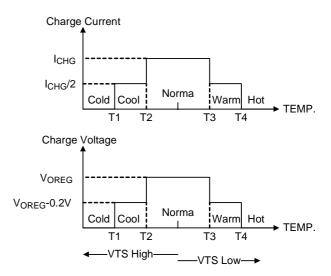

#### TS Detection

The RT9466 detects the temperature of the battery pack via REGN and TS pins. The REGN pin provides a constant voltage source to drive the voltage divider composed of a pulled-high resister and a NTC resister. The RT9466 reports the sensing results via IRQ and status bits for COLD, COOL, WARM and HOT.

#### I<sup>2</sup>C Controller

The key parameters of charging and OTG are programmable through  $I^2C$  commands.

## Absolute Maximum Ratings (Note 1)

| , , , , , , , , , , , , , , , , , , , ,                                     |                                               |

|-----------------------------------------------------------------------------|-----------------------------------------------|

| Supply Input Voltage, VBUS                                                  |                                               |

| • Supply Input Voltage, VBUS (Peak <100ns duration)                         |                                               |

| • VMID, BTST                                                                |                                               |

| • LX                                                                        | -0.3V to 16V                                  |

| • LX (Peak <100ns duration)                                                 | -2V                                           |

| • VMID – VBUS, BTST – LX                                                    | -0.3V to 6V                                   |

| • Other Pins                                                                | -0.3V to 6V                                   |

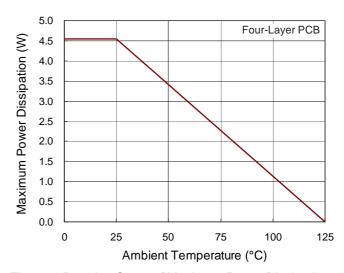

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                                               |

| WQFN-24L 4x4                                                                | 4.54W                                         |

| Package Thermal Resistance (Note 2)                                         |                                               |

| WQFN-24L 4x4, $\theta_{JA}$                                                 | 22°C/W                                        |

| WQFN-24L 4x4, $\theta_{JC}$                                                 | 5.4°C/W                                       |

| • Lead Temperature (Soldering, 10 sec.)                                     | 260°C                                         |

| • Junction Temperature                                                      | 150°C                                         |

| Storage Temperature Range                                                   | –65°C to 150°C                                |

| ESD Susceptibility (Note 3)                                                 |                                               |

| HBM (Human Body Model)                                                      | 2kV                                           |

| Decommended Operating Conditions (1)                                        |                                               |

| Recommended Operating Conditions (Note 4)                                   |                                               |

| • Supply Input Voltage                                                      | 4V to 14V                                     |

| Maximum Input Current (VBUS), I <sub>AICR</sub>                             | 3.25A                                         |

| Maximum SYS Output Current (SW), I <sub>SYS</sub>                           | 5A                                            |

| Maximum Battery Voltage, VBAT                                               | 4.71V                                         |

| Maximum I <sub>BAT</sub> Fast Charging Current                              | 5A                                            |

| Maximum I <sub>BAT</sub> Discharging Current                                | 6A                                            |

| Maximum I <sub>BAT</sub> Discharging Current peak,1sec duration             | 9A                                            |

| • Junction Temperature Range                                                |                                               |

| Ambient Temperature Range                                                   | $-40^{\circ}\text{C}$ to $85^{\circ}\text{C}$ |

|                                                                             |                                               |

### **Electrical Characteristics**

$(V_{BUS}=5V,\,V_{BAT}=4.2V,\,L=1\mu H,\,C_{IN}=2.2\mu F,\,C_{BATS}=10\mu F,\,T_{A}=25^{\circ}C,\,unless\,\,otherwise\,\,specified)$

| Parameter                               | Symbol        | Test Conditions                                                                               | Min | Тур | Max | Unit |

|-----------------------------------------|---------------|-----------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Quiescent Current                       |               |                                                                                               |     |     |     |      |

| V <sub>BUS</sub> Supply Current         | Ivbus_sw      | V <sub>LX</sub> is switching, V <sub>BUS</sub> = 5V, V <sub>SYS</sub> = 3.8V                  |     | 8   |     | mA   |

|                                         | Ivbus_non_sw  | $V_{LX}$ Is non-switching, $V_{BUS} = 5V$ , $V_{SYS} = 4.4V$                                  |     |     | 5   | mA   |

|                                         | Ivbus_Hz      | V <sub>LX</sub> is in high-impendence mode,<br>V <sub>BUS</sub> = 5V, V <sub>SYS</sub> = 3.8V |     |     | 170 | μА   |

| Pottory Lookogo Current                 | IBAT_LEAK_OFF | V <sub>BAT</sub> = 4.2V, power path is off                                                    |     |     | 25  | μА   |

| Battery Leakage Current                 | IBAT_LEAK_ON  | V <sub>BAT</sub> = 4.2V                                                                       |     |     | 60  | μА   |

| Boost-Mode Battery<br>Discharge Current | IBAT_BOOST_SW | V <sub>BAT</sub> = 4.2V, boost mode, I <sub>VBUS</sub> = 0A, V <sub>LX</sub> is switching     |     | 5   |     | mA   |

| Parameter                                                         | Symbol                    | Test Conditions                                                          | Min  | Тур  | Max  | Unit |

|-------------------------------------------------------------------|---------------------------|--------------------------------------------------------------------------|------|------|------|------|

| V <sub>BUS</sub> / V <sub>BAT</sub> Power-Up                      |                           |                                                                          |      |      |      |      |

| Sleep-Mode Entry<br>Threshold, V <sub>BUS</sub> -V <sub>BAT</sub> | V <sub>SLEEP_ENTER</sub>  | 2.5V < V <sub>BAT</sub> < V <sub>OREG</sub> , V <sub>BUS</sub> falling   | 0    | 40   | 100  | mV   |

| Sleep-Mode Exit<br>Threshold, V <sub>BUS</sub> -V <sub>BAT</sub>  | V <sub>SLEEP_EXIT</sub>   | 2.5V < V <sub>BAT</sub> < V <sub>OREG</sub> , V <sub>BUS</sub> rising    | 40   | 100  | 200  | mV   |

| Sleep-Mode Exit Deglitch<br>Time                                  | t <sub>D_SLEEP_EXIT</sub> | Exit sleep-mode                                                          | 1    | 120  |      | ms   |

| V <sub>BUS</sub> Bad Adapter<br>Threshold                         | V <sub>BAD_ADP</sub>      |                                                                          | 1    | 3.8  |      | V    |

| V <sub>BUS</sub> Bad Adapter<br>Hysteresis                        | V <sub>BAD_ADP_HYS</sub>  |                                                                          | -    | 150  |      | mV   |

| V <sub>BUS</sub> Bad Adapter Sink<br>Current                      | I <sub>BAD_ADP_SINK</sub> |                                                                          |      | 50   |      | mA   |

| V <sub>BUS</sub> Bad Adapter<br>Detection Time                    | tBAD_ADP_DET              |                                                                          |      | 30   |      | ms   |

| Input Current Limit Factor                                        | K <sub>ILIM</sub>         | Input current regulation 508mA by ILIM pin with resistance = $698\Omega$ | 320  | 355  | 390  | ΑΩ   |

| Input Current Limit<br>Regulation                                 | I <sub>ILIM_MIN</sub>     | Minimum input current for regulation on ILIM pin                         | 0.5  |      |      | А    |

| Input Power Regulation                                            |                           |                                                                          |      |      |      |      |

| Minimum Input Voltage<br>Regulation (MIVR)<br>Threshold Range     | VMIVR                     | I <sup>2</sup> C programmable in 0.1V steps                              | 3.9  |      | 13.4 | V    |

| Default Minimum Input<br>Voltage Regulation<br>Threshold          | V <sub>MIVR_DEF</sub>     | Default                                                                  |      | 4.4  |      | ٧    |

| Minimum Input Voltage<br>Regulation Accuracy                      | VMIVR_ACC                 | VMIVR = 4.4V, 9V                                                         | -3   | 1    | 3    | %    |

|                                                                   |                           | USB charge mode, IAICR = 100mA                                           | 86   | 93   | 100  | mΛ   |

|                                                                   |                           | USB charge mode, I <sub>AICR</sub> = 500mA                               | 440  | 470  | 500  | mA   |

| Average Input Current Regulation Accuracy                         | I <sub>AICR_ACC</sub>     | USB charge mode,<br>I <sub>AICR</sub> = 1000mA                           | 880  | 940  | 1000 | mA   |

|                                                                   |                           | Adapter 1.5A charge mode,<br>I <sub>AICR</sub> = 1500mA                  | 1300 | 1400 | 1500 | mA   |

| Protection                                                        |                           |                                                                          |      |      |      |      |

| V <sub>BUS</sub>                                                  |                           |                                                                          |      |      |      |      |

| V <sub>BUS</sub> Under-Voltage<br>Protection Threshold            | Vuvlo                     | V <sub>BUS</sub> rising                                                  | 3.05 | 3.3  | 3.55 | V    |

| V <sub>BUS</sub> Under-Voltage<br>Protection Hysteresis           | Vuvlo_HYS                 | V <sub>BUS</sub> falling from UVLO                                       |      | 150  |      | mV   |

| V <sub>BUS</sub> Over-Voltage<br>Protection Threshold             | VBUS_OVP                  | V <sub>BU</sub> s rising                                                 | 13.5 | 14.5 | 15.5 | V    |

| V <sub>BUS</sub> Over-Voltage<br>Protection Hysteresis            | V <sub>BUS_OVP_HYS</sub>  | V <sub>BUS</sub> falling                                                 |      | 250  |      | mV   |

DS9466-02 February 2017

7

| Parameter                                             | Symbol               |                                                 | Test Conditions                                      | Min | Тур  | Max  | Unit |

|-------------------------------------------------------|----------------------|-------------------------------------------------|------------------------------------------------------|-----|------|------|------|

| V <sub>BAT</sub>                                      |                      | -1                                              |                                                      |     |      |      |      |

| Battery Over-Voltage<br>Protection Threshold          | VBAT_OVP             | Voreg, a                                        | ng, as percentage of<br>as<br>/P-Voreg)/Voreg        | 106 | 108  | 110  | %    |

| Battery Over-Voltage<br>Protection Hysteresis         | VBAT_OVP_HYS         | V <sub>BAT</sub> falli<br>(V <sub>BAT_O</sub> ) | ing, as<br>/P_HYS)/Voreg                             |     | 4    |      | %    |

| Thermal Protection                                    |                      |                                                 |                                                      |     |      |      |      |

| Over-Temperature Protection Threshold                 | Тотр                 | Thermal temperat                                | shutdown threshold<br>ture                           |     | 160  |      | °C   |

| Over-Temperature<br>Protection Hysteresis             | T <sub>OTP_HYS</sub> | Thermal temperat                                | shutdown hysteresis<br>ture                          |     | 30   |      | °C   |

| Thermal Regulation<br>Threshold                       | T <sub>TR</sub>      | Charge o                                        | current starts decreasing                            |     | 120  |      | °C   |

| V <sub>SYS</sub>                                      |                      |                                                 |                                                      |     |      |      |      |

| V <sub>SYS</sub> Over-Voltage<br>Protection Threshold | Vsys_ovp             | V <sub>SYS</sub> risi                           | ng                                                   |     | 5.25 |      | V    |

| Vsys Under-Voltage<br>Protection Threshold            | Vsys_uvp             | V <sub>SYS</sub> fall                           | ing                                                  |     | 2.4  |      | V    |

| <b>Battery Charging Stages</b>                        |                      |                                                 |                                                      |     |      |      |      |

| End of Charge                                         | 1                    | _                                               |                                                      | ,   |      | _    |      |

| Regulated Battery Voltage Range                       | Voreg                | I <sup>2</sup> C prog                           | rammable in 10mV steps                               | 3.9 | -    | 4.71 | V    |

| Regulated Battery Voltage                             | Voreg_def            | Default                                         |                                                      |     | 4.2  |      | V    |

| Regulated Battery Voltage Accuracy                    | Voreg_acc            | Tempera                                         | ature = 0°C to 85°C                                  | -1  | 1    | 1    | %    |

| Re-Charge Mode<br>Threshold                           | VRECH                |                                                 | ing, the difference below<br>, (Addr 0x0B[2:0] = 00) | 50  | 100  | 150  | mV   |

| Re-Charge Deglitch Time                               | tD_RECH              |                                                 |                                                      |     | 120  |      | ms   |

| End-of-Charge Current                                 | I <sub>EOC</sub>     | I <sup>2</sup> C progi                          | rammable in 50mA steps                               | 100 |      | 850  | mA   |

| Default End-of-Charge<br>Current                      | IEOC_DEF             | Default                                         |                                                      |     | 250  |      | mA   |

| End-of-Charge Current<br>Accuracy                     | IEOC_ACC             |                                                 |                                                      | -20 | 1    | 20   | %    |

| Default End-of-Charge<br>Deglitch Time                | t <sub>D_EOC</sub>   | Default                                         |                                                      |     | 2    |      | ms   |

| Fast Charge                                           |                      |                                                 |                                                      |     |      |      |      |

| Charge Current Range                                  | I <sub>CHG</sub>     | I <sup>2</sup> C progr                          | rammable in 0.1A steps                               | 0.1 |      | 5    | Α    |

|                                                       |                      |                                                 | I <sub>CHG</sub> < 500mA                             | -20 |      | 20   | %    |

| Charge Current Accuracy                               | I <sub>CHG_ACC</sub> | V <sub>BAT</sub> = 3.8V                         | 500mA < I <sub>CHG</sub> < 1000mA                    | -10 |      | 10   | %    |

|                                                       |                      |                                                 | I <sub>CHG</sub> > 1000mA                            | -7  |      | 7    | %    |

| Parameter                             | Symbol                  | Test Conditions                                                                 | Min | Тур  | Max | Unit |

|---------------------------------------|-------------------------|---------------------------------------------------------------------------------|-----|------|-----|------|

| Pre-Charge                            |                         |                                                                                 |     |      |     | •    |

| Pre-Charge Mode<br>Threshold          | VPRECHG                 | I <sup>2</sup> C programmable in 0.1V steps                                     | 2   | 1    | 3.5 | V    |

| Pre-Charge Mode<br>Hysteresis         | VPRECHG_HYS             | Pre-charge hysteresis                                                           |     | 0.2  |     | V    |

| Pre-Charge Mode<br>Threshold Accuracy | VPRECHG_ACC             |                                                                                 | -5  | 1    | 5   | %    |

| Pre-Charge Current Range              | I <sub>PRECHG</sub>     | I <sup>2</sup> C programmable in 50mA steps                                     | 100 | 1    | 850 | mA   |

| Default Pre-Charge Current            | I <sub>PRECHG_DEF</sub> | Default                                                                         |     | 150  |     | mA   |

| Pre-Charge Current<br>Accuracy        | I <sub>PREC_</sub> ACC  |                                                                                 | -20 | 1    | 20  | %    |

| Trickle charge                        |                         |                                                                                 |     |      |     |      |

| Trickle Charge Threshold              | VTRICHG                 | VBAT falling                                                                    |     | 2    |     | V    |

| Trickle Charge Threshold Hysteresis   | VTRICHG_Hys             | VBAT rising                                                                     |     | 200  | -   | mV   |

| Trickle Charge Threshold accuracy     | VTRICHG_acc             |                                                                                 | -5  | 1    | 5   | %    |

| Trickle Current                       | ITRICHG                 | VBAT< 2V,<br>charge with ICC = 100mA<br>VBAT < 1.6V,<br>charge with AICR =100mA |     | 100  |     | mA   |

| Trickle Current Accuracy              | I <sub>TRICHG_acc</sub> |                                                                                 | -20 |      | 20  | %    |

| V <sub>SYS</sub>                      |                         |                                                                                 |     |      |     |      |

| System Regulation Voltage             | Vsysreg                 | Minimum system regulation voltage, I <sup>2</sup> C programmable in 0.1V steps  | 3.3 |      | 4   | V    |

| Default System Regulation Voltage     | Vsysreg_def             | Default minimum system regulation voltage                                       |     | 3.6  |     | V    |

| System Regulation<br>Accuracy         | Vsysreg_ acc            |                                                                                 | -5  |      | 5   | %    |

| Battery Charger                       |                         |                                                                                 |     |      |     |      |

| UUG On-Resistance                     | Ron_uug                 | From VBUS to VMID                                                               |     | 17   | 32  | mΩ   |

| High-Side On-Resistance               | Ron_uug_ug              | From VBUS to LX                                                                 |     | 42   | 79  | mΩ   |

| Low-Side On-Resistance                | R <sub>ON_LG</sub>      | From LX to PGND                                                                 |     | 28   | 40  | mΩ   |

| Power-Path-Side<br>On-Resistance      | RON_PPMOS               | From SYS to BAT                                                                 |     | 13   | 30  | mΩ   |

| Switching Frequency (1.5MHz)          | fosc1                   | I <sup>2</sup> C programmable to 1.5 MHz (Addr 0x01[7] =0)                      |     | 1.5  | -   | MHz  |

| Switching Frequency<br>(750kHz)       | fosc2                   | I <sup>2</sup> C programmable to 0.75MHz<br>(Addr 0x01[7] =1)                   |     | 0.75 |     | MHz  |

| Frequency Accuracy                    | fosc_acc                |                                                                                 | -10 |      | 10  | %    |

| Maximum Duty Cycle                    | D <sub>MAX</sub>        | At minimum input voltage                                                        |     | 97   |     | %    |

| Minimum Duty Cycle                    | D <sub>MIN</sub>        |                                                                                 | 0   |      |     | %    |

| Parameter                                                   | Symbol                  | Test Conditions                                        | Min       | Тур  | Max   | Unit |

|-------------------------------------------------------------|-------------------------|--------------------------------------------------------|-----------|------|-------|------|

| REGN Regulation                                             | V <sub>REGN</sub>       | V <sub>BUS</sub> = 5V / 9V / 12V                       |           | 4.9  |       | V    |

| REGN Current Limit                                          | ILIM_REGN               | V <sub>BUS</sub> = 5V / 9V / 12V                       | 50        |      |       | mA   |

| Sink Current for Battery Detection                          | IBAT_SINK               |                                                        |           | 300  |       | μА   |

| Internal QON Pull-Up<br>Resistance                          | $R_{\overline{QON}}$    |                                                        |           | 200  |       | kΩ   |

| Internal OON Dull 1 In                                      | \/                      | Battery only                                           |           | VBAT |       | V    |

| Internal QON Pull-Up                                        | $V_{\overline{QON}}$    | V <sub>BUS</sub> = 5V/9V                               |           | 4.8  |       | ľ    |

| QON Exit Shipping Mode Time                                 | tSHIPMODE               | QON Low for BATFET on-time to exit shipping mode       |           | 0.9  | 1     | sec  |

| System Reset by QON Pin                                     | t <sub>QON_</sub> RST   | QON low time to enable full system reset               |           | 10   | 1     | sec  |

| BATFET Reset Time                                           | tbatfet_rst             | BATFET off-time during full system reset               |           | 0.41 | 1     | sec  |

| Shipping Mode Entry<br>Deglitch Time                        | t <sub>D_SM_ENTER</sub> | Enter shipping mode                                    |           | 9    | 1     | sec  |

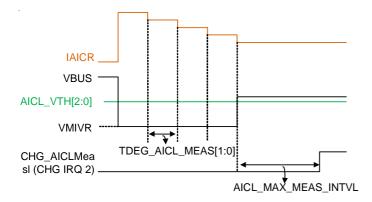

| AICL                                                        | VAICL                   | V <sub>BUS</sub> rising, I <sup>2</sup> C programmable |           | 4.6  | 1     | V    |

| AICL Hysteresis                                             | VAICL_HYS               |                                                        |           | 50   | ŀ     | mV   |

| Inductor Over-Current<br>Protection Buck Threshold          | I <sub>OCP_BUCK</sub>   | Inductor OCP level for buck mode                       |           | 6    |       | А    |

| OTG Boost Mode Operation                                    | on                      |                                                        |           |      |       |      |

| OTG Boost-Mode Output<br>Regulation Voltage Range           | Votgbst                 | To VBUS                                                | 4.425     |      | 5.825 | V    |

| OTG Boost-Mode Output<br>Regulation Voltage<br>Accuracy     | Votgbst_acc             |                                                        | -3        |      | 3     | %    |

| OTG Boost-Mode<br>Over-Load Protection<br>Threshold         | IOTG_OLP                | I <sup>2</sup> C programmable                          | 0.5       |      | 2.4   | А    |

| OTG Boost-Mode Default<br>Over-Load Protection<br>Threshold | IOTG_OLP_DEF            | Addr 0x0A [2:0] = 000                                  | 0.5       |      | 1     | Α    |

| OTG Low Battery<br>Protection Threshold                     | VOTG_LBP                | I <sup>2</sup> C programmable,<br>hysteresis = 0.4 V   | 2.3       |      | 3.8   | V    |

| OTG Default Low Battery<br>Protection Threshold             | VOTG_LBP_DEF            | OTG_LBP = 2.8V (Addr0x0A[7:4]<br>= 0101)               |           | 2.8  |       | V    |

| OTG Low Battery<br>Protection Threshold<br>Accuracy         |                         |                                                        | <b>-5</b> |      | 5     | %    |

| OTG VMID Over-Voltage Protection                            | VOTG_VMID_OVP           | V <sub>VMID</sub> rising                               |           | 6    | -     | V    |

| OTG VMID Over-Voltage<br>Protection Hysteresis              | VOTG_VMID_OVP_<br>HYS   |                                                        |           | 200  |       | mV   |

| Parameter                                           | Symbol                 | Test Conditions                                         | Min  | Тур  | Max  | Unit |

|-----------------------------------------------------|------------------------|---------------------------------------------------------|------|------|------|------|

| Inductor Over-Current<br>Protection Boost Threshold | I <sub>OCP_BOOST</sub> | Inductor OCP level for boost mode                       |      | 5.5  | 1    | Α    |

| Current Pulse Control, PE                           | 1.0                    |                                                         |      |      |      |      |

| Current Pulse Control Stop<br>Pulse                 | tPUMPX_STOP            |                                                         | 430  |      | 570  | ms   |

| Current Pulse Control Long<br>On Pulse              | tPUMPX_ON1             |                                                         | 240  | 1    | 360  | ms   |

| Current Pulse Control Short<br>On Pulse             | tPUMPX_ON2             |                                                         | 70   | ŀ    | 130  | ms   |

| Current Pulse Control Off<br>Pulse                  | t <sub>PUMPX_OFF</sub> |                                                         | 70   | -    | 130  | ms   |

| Current Pulse Control Stop<br>Start Delay           | tPUMPX_DLY             |                                                         | 80   |      | 225  | ms   |

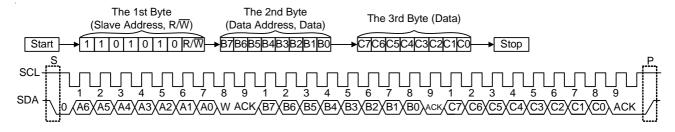

| I <sup>2</sup> C Characteristics                    |                        |                                                         |      |      |      |      |

| Output Low Threshold<br>Voltage                     | V <sub>OL_I2C</sub>    | I <sub>DS</sub> = 10mA                                  |      |      | 0.4  | V    |

| SCL, SDA Input Logic High<br>Threshold Voltage      | VIH_I2C                |                                                         | 1.3  |      |      | V    |

| SCL, SDA Input Logic Low<br>Threshold Voltage       | VIL_I2C                |                                                         |      |      | 0.4  | V    |

| SCL Clock                                           | f <sub>SCL</sub>       |                                                         |      |      | 400  | kHz  |

| High Level Leakage<br>Current                       | I <sub>BIRS</sub>      | V <sub>PULL_UP</sub> = 1.8V, SDA and SCL                |      |      | 1    | μА   |

| Load Capacitance                                    | CLOAD                  | V <sub>PULL_UP</sub> = 1.8V                             |      |      | 1    | pF   |

| Default Wait Time for<br>Watch Dog Reset            | twdt_def               | Watch Dog timer selection,<br>Default : 0x0D[6] = 1     |      | 500  |      | ms   |

| NTC Monitor                                         |                        |                                                         |      |      |      |      |

| Battery Temperature HOT Threshold                   | Vvts_hot               | V <sub>TS</sub> falling, the ratio of V <sub>REGN</sub> | 33.5 | 34.5 | 35.5 | %    |

| Battery Temperature<br>WARM Threshold               | Vvts_warm              | VTS falling, the ratio of VREGN                         | 44   | 45   | 46   | %    |

| Battery Temperature COOL<br>Threshold               | Vvts_cool              | V <sub>TS</sub> rising, the ratio of V <sub>REGN</sub>  | 67.5 | 68.5 | 69.5 | %    |

| Battery Temperature COLD Threshold                  | VVTS_COLD              | V <sub>TS</sub> rising, the ratio of V <sub>REGN</sub>  | 72.5 | 73.5 | 74.5 | %    |

| Battery Temperature<br>Hysteresis                   | Vvts_Hys               |                                                         |      | 2    |      | %    |

| Control I/O Pin (STAT, PG,                          | INT)                   |                                                         |      |      |      |      |

| Output Low Voltage                                  | Vol_ctrl               | I <sub>DS</sub> = 10mA                                  |      |      | 0.4  | V    |

| Control I/O Pin (OTG, CEB                           | , PSEL, QON)           |                                                         |      |      |      |      |

| Input Throshold Valtage                             | VIH_CTRL               | Logic High Threshold                                    | 1.3  |      |      | \/   |

| Input Threshold Voltage                             | VIL_CTRL               | Logic Low Threshold                                     |      |      | 0.4  | V    |

DS9466-02 February 2017

| Parameter                            | Symbol                      | Test Conditions      | Min | Тур  | Max  | Unit |

|--------------------------------------|-----------------------------|----------------------|-----|------|------|------|

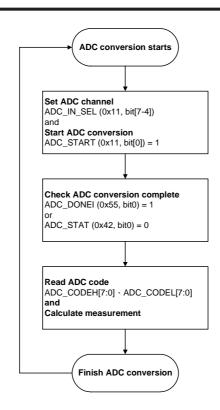

| ADC                                  |                             |                      |     |      |      |      |

| ADC Conversion Time each Channel     | tCONV                       |                      | 35  | 200  |      | ms   |

| Number of Bits for ADC<br>Resolution | RES                         | Logic High Threshold |     | 10   |      | bit  |

| ADC Accuracy and Measur              | rement Range                |                      |     |      |      |      |

| VBUS_DIV5 Measurement Range          | VvBUS_DIV5ADC_R ange        |                      | 1   |      | 22   | V    |

| VBUS_DIV5 Resolution                 | VVBUS_DIV5ADC_R<br>ES       |                      |     | 25   |      | mV   |

| VBUS_DIV5 Accuracy                   | VVBUS_DIV5ADC_A             |                      | -2  |      | 2    | LSB  |

| VBUS_DIV2 Measurement Range          | VvBUS_DIV2ADC_R ange        |                      | 1   |      | 9.8  | V    |

| VBUS_DIV2 Resolution                 | Vvbus_div2adc_r<br>es       |                      |     | 10   |      | mV   |

| VBUS_DIV2 Accuracy                   | Vvbus_div2adc_a             |                      | -2  |      | 2    | LSB  |

| VBAT Measurement Range               | VVBAT ADC_Range             |                      | 0   |      | 4.9  | ٧    |

| VBAT Resolution                      | VVBAT ADC_RES               |                      |     | 5    |      | mV   |

| VBAT Accuracy                        | VVBAT ADC_ACC               |                      | -2  |      | 2    | LSB  |

| VSYS Measurement Range               | VVSYS ADC_Range             |                      | 0   |      | 4.9  | V    |

| VSYS Resolution                      | VVSYS ADC_RES               |                      |     | 5    |      | mV   |

| VSYS Accuracy                        | VVSYS ADC_ACC               |                      | -2  |      | 2    | LSB  |

| REGN Measurement<br>Range            | VREGN ADC_Range             |                      | 0   |      | 4.9  | V    |

| REGN Resolution                      | VREGN ADC_RES               |                      |     | 5    |      | mV   |

| REGN Accuracy                        | VREGN ADC_ACC               |                      | -2  |      | 2    | LSB  |

| TS_BAT Measurement Range             | Rate <sub>TS_BAT</sub>      |                      | 0   |      | 100  | %    |

| TS_BAT Resolution                    | Raters_BAT_RES              |                      |     | 0.25 |      | %    |

| TS_BAT Accuracy                      | Raters_BAT ACC              |                      | -2  |      | 2    | LSB  |

| IBUS Measurement Range               | IBUS ADC_Range              |                      | 0   |      | 3.25 | Α    |

| IBUS Resolution                      | IIBUS ADC_RES               |                      |     | 50   |      | mA   |

| IBUS Accuracy                        | IBUS ADC_ACC                |                      | -2  |      | 2    | LSB  |

| IBAT Measurement Range               | I <sub>IBAT</sub> ADC_Range |                      | 0   |      | 5    | Α    |

| IBAT Resolution                      | IIBAT ADC_RES               |                      |     | 50   |      | mA   |

| IBAT Accuracy                        | IBAT ADC_ACC                |                      | -2  |      | 2    | LSB  |

| Parameter                 | Symbol                             | Test Conditions     | Min | Тур | Max | Unit |

|---------------------------|------------------------------------|---------------------|-----|-----|-----|------|

| TEMP_JC Measurement Range | T <sub>TEMP</sub> _JC<br>ADC_Range |                     | -40 |     | 120 | °C   |

| TEMP_JC Resolution        | T <sub>TEMP_JC</sub> ADC_RES       |                     |     | 2   |     | °C   |

| TEMP_JC Accuracy          | TTEMP_JC<br>ADC_ACC                | Temperature < 85 °C | -2  |     | 2   | LSB  |

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25$ °C on a Four-layer Richtek Evaluation Board.  $\theta_{JC}$  is measured at the Top of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

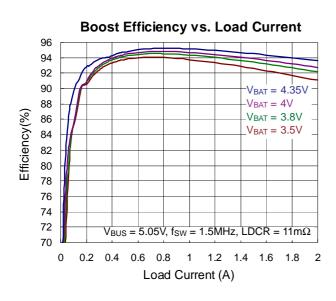

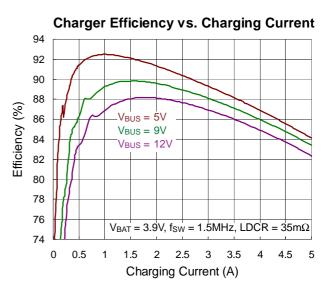

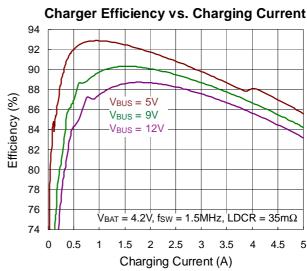

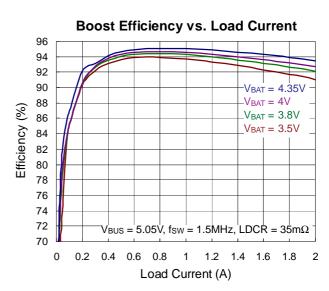

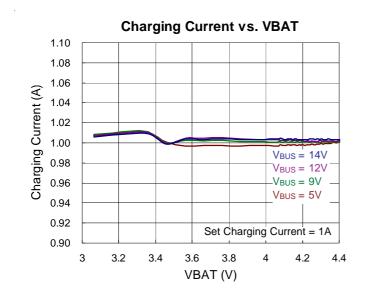

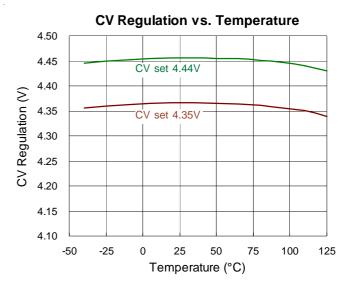

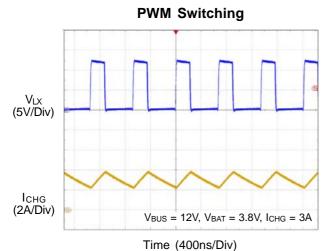

### **Typical Operating Characteristics**

DS9466-02 February 2017

www.richtek.com

# **Register Descriptions**

**I<sup>2</sup>C Slave Address**: 1010011 (53H)

| Na         | me   | Function  | Addr        | Reset                                                                                                                                                                                                                                            |

|------------|------|-----------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CORE_CTRL0 |      | Control 0 | 0x00        | 0x00                                                                                                                                                                                                                                             |

| Bit        | Mode | Name      | Reset Value | Description                                                                                                                                                                                                                                      |

| 7          | R/W  | RST_REG   | 0           | All registers reset bit. 0: Don't reset all registers. 1: Reset all registers. (Notice: 1. This bit will be reset to "0" after reset procedure finish. 2. In high-impedance mode, this bit reset all registers after leave high-impedance mode.) |

| [6:0]      | R/W  | Reversed  | 0000000     | Reversed                                                                                                                                                                                                                                         |

| Na   | me    | Function   | Addr        | Reset                                                                                                                                                                                                              |

|------|-------|------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHG_ | CTRL1 | Control 1  | 0x01        | 0x10                                                                                                                                                                                                               |

| Bit  | Mode  | Name       | Reset Value | Description                                                                                                                                                                                                        |

| 7    | R/W   | SEL_SWFREQ | 0           | The switching frequency selection bit (Charger/OTG) 0: The switching frequency is 1.5MHz. (Default) 1: The switching frequency is 0.75MHz.                                                                         |

| 6    | R/W   | FIXFREQ    | 0           | Charger switching frequency 0 : Charger switching frequency would be varied if VBUS is closed to VBAT(default) 1 : Charger switching frequency is fixed                                                            |

| 5    | R/W   | Reversed   | 0           | Reversed                                                                                                                                                                                                           |

| 4    | R/W   | STAT_EN    | 1           | Charger STAT pin function 0 : Disable 1 : Enable (default)                                                                                                                                                         |

| 3    | R/W   | IRQ_PULSE  | 0           | IRQ reminder function 0: IRQ reminder is disabled (default) 1: IRQ reminder is enabled. If IRQ is triggered but no check action, INT pin will be released as well as being triggered again with every 2s intervals |

| 2    | R/W   | HZ         | 0           | High-impedance selection 0 : No high-impedance mode (default) 1 : High-impedance mode                                                                                                                              |

| 1    | R/W   | OTG_PIN_EN | 0           | Boost mode enable with OTG pin 0 : Enable Boost mode by OPA_MODE (default) 1 : Enable Boost by both OPA_MODE bit and OTG pin                                                                                       |

| 0    | R/W   | OPA_MODE   | 0           | Boost mode enable 0 : Charge mode (default) 1 : Boost mode for OTG                                                                                                                                                 |

| Na    | me     | Function          | Addr        | Reset                                                                                                                                                                                  |

|-------|--------|-------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHG ( | CTRL 2 | Charger Control 2 | 0x02        | 0x03                                                                                                                                                                                   |

| Bit   | Mode   | Name              | Reset Value | Description                                                                                                                                                                            |

| 7     | R/W    | SHIP_MODE         | 0           | Shipping mode enable, force BATFET OFF 0 : Allow BATFET turn on (default) 1 : Force BATFET turn off                                                                                    |

| 6     | R/W    | BATDET_DIS_DLY    | 0           | BATFET turn off delay 0 : BATFET turn off immediately (default) 1 : BATFET turn off with 10s delay after SHIP_MODE bit is set                                                          |

| 5     | R/W    | Reserved          | 0           | Reserved                                                                                                                                                                               |

| 4     | R/W    | TE                | 0           | Termination enable 0 : Disable charge current termination (default) 1 : Enable charge current termination                                                                              |

| [3:2] | R/W    | IINLMTSEL         | 00          | Input current limit selection bit 00 : PSEL pin result is applied (default) 01 : Reserved 10 : IAICR[5:0] results is applied 11 : Input limit is set by the lower level of these three |

| 1     | R/W    | CFO_EN            | 1           | Charger and OTG enable 0 : CFO is disabled 1 : CFO is enabled (default)                                                                                                                |

| 0     | R/W    | CHG_EN            | 1           | Charger and Boost enable 0 : Charger and Boost is disabled 1 : Charger and Boost is enabled (default)                                                                                  |

| N     | lame  | Function   | Addr        | Reset                                                                                                                                                   |

|-------|-------|------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHG   | CTRL3 | Control 3  | 0x03        | 0x23                                                                                                                                                    |

| Bit   | Mode  | Name       | Reset Value | Description                                                                                                                                             |

| [7:2] | R/W   | IAICR[5:0] | 001000      | AICR setting 000000 : 100mA 000001 : 150mA 000010 : 200mA 000011 : 250mA 001000 : 500mA (default) 001001 : 550mA 100110 : 2A 111010 : 3A 111111 : 3.25A |

| 1     | R/W   | AICR_EN    | 1           | AICR loop enable 0 : AICR loop disable 1 : AICR loop enable (default)                                                                                   |

| 0     | R/W   | ILIM_EN    | 1           | ILIM function enable 0 : ILIM function disable 1 : ILIM function enable (default)                                                                       |

| N     | lame   | Function   | Addr        | Reset                                                                                                                                                                                                                                                                                                |

|-------|--------|------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHG   | _CTRL4 | Control 4  | 0x04        | 0x3C                                                                                                                                                                                                                                                                                                 |

| Bit   | Mode   | Name       | Reset Value | Description                                                                                                                                                                                                                                                                                          |

| [7:1] | R/W    | VOREG[6:0] | 0011110     | Battery regulation voltage. The delta-V of the Battery regulation voltage is 10mV. 0000000 : 3.9V 0000001 : 3.91V 0000010 : 3.92V 0000011 : 3.93V 0011101 : 4.19V 0011110 : 4.2V (default) 0011111 : 4.21V 0101100 : 4.34V 0101101 : 4.35V 0101110 : 4.36V 1010001 : 4.71V 1010001 ~ 1111111 : 4.71V |

| 0     | R/W    | Reserved   | 0           | Reserved                                                                                                                                                                                                                                                                                             |

| N     | lame  | Function     | Addr        | Reset                                                                                                                                                                                                                                                             |

|-------|-------|--------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHG   | CTRL5 | Control 5    | 0x05        | 0x67                                                                                                                                                                                                                                                              |

| Bit   | Mode  | Name         | Reset Value | Description                                                                                                                                                                                                                                                       |

| [7:2] | R/W   | VOTGBST[5:0] | 011001      | OTG boost-mode output regulation voltage. The delta-V of the OTG regulation voltage is 25mV.  000000 : 4.425V  000001 : 4.45V  000010 : 4.475V  010111 : 5V  011000 : 5.025V  011001 : 5.05V (default)  011011 : 5.1V  111000 : 5.825V  111001 to 111111 : 5.825V |

| [1:0] | R/W   | THREG[1:0]   | 11          | Charger thermal regulation threshold<br>00 : 60°C<br>01 : 80°C<br>10 : 100°C<br>11 : 120°C (default)                                                                                                                                                              |

| N     | lame  | Function   | Addr        | Reset                                                                                                                                                                                                                                                                           |

|-------|-------|------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHG   | CTRL6 | Control 6  | 0x06        | 0x0B                                                                                                                                                                                                                                                                            |

| Bit   | Mode  | Name       | Reset Value | Description                                                                                                                                                                                                                                                                     |

| [7:1] | R/W   | VMIVR[6:0] | 0000101     | Input MIVR threshold setting 0000000 : 3.9V 0000001 : 4V 0000010 : 4.1V 0000010 : 4.3V 0000100 : 4.3V 0000101 : 4.4V (default) 0000110 : 4.5V 0011110 : 6.9V 0011111 : 7V 0110010 : 8.9V 0110011 : 9V 1010000 : 11.9V 1010001 : 12V 1011111 : 13.4V 1100000 to 11111111 : 13.4V |

| 0     | R/W   | MIVR_EN    | 1           | MIVR loop enable 0: MIVR loop disable 1: MIVR loop enable (default)                                                                                                                                                                                                             |

| N     | lame   | Function       | Addr        | Reset                                                                                                                                                                                                                                                                                                                     |

|-------|--------|----------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHG   | _CTRL7 | Control 7      | 0x07        | 0x4C                                                                                                                                                                                                                                                                                                                      |

| Bit   | Mode   | Name           | Reset Value | Description                                                                                                                                                                                                                                                                                                               |

| [7:2] | R/W    | ICHG[5:0]      | 010011      | Charging regulation current 000000: 0.1A 000001: 0.2A 000010: 0.3A 001000: 0.9A 001001: 1A 001010: 1.1A 010010: 1.9A 010011: 2A (default) 011100: 2.9A 011101: 3A 100110: 3.9A 100111: 4A 110000: 4.9A 110010: to 111111: 5A Note: When ICHG is set above 2.5A, recommend the OCP to set higher level. (Addr 0x0D[2] = 1) |

| [1:0] | R/W    | EOC_TIMER[1:0] | 00          | EOC back-charging time 00 : 0mins (default) 01 : 30mins 10 : 45mins 11 : 60mins                                                                                                                                                                                                                                           |

| Nar   | ne    | Function   | Addr        | Reset                                                                                                                                                                                                                |

|-------|-------|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHG_C | CTRL8 | Control 8  | 0x08        | 0xA1                                                                                                                                                                                                                 |

| Bit   | Mode  | Name       | Reset Value | Description                                                                                                                                                                                                          |

| [7:4] | R/W   | VPREC[3:0] | 1010        | Pre-Charge voltage threshold 0000: 2V 0001: 2.1V 0010: 2.2V 0011: 2.3V 0100: 2.4V 0101: 2.5V 0110: 2.6V 0111: 2.7V 1000: 2.8V 1001: 2.9V 1010: 3.0V (default) 1011: 3.1V 1100: 3.2V 1101: 3.3V 1110: 3.4V 1111: 3.5V |

| [3:0] | R/W   | IPREC[3:0] | 0001        | Pre-Charge current threshold 0000: 100mA 0001: 150mA (default) 0010: 200mA 0011: 250mA 0100: 300mA 0101: 350mA 0110: 400mA 0111: 450mA 1000: 500mA 1001: 550mA 1010: 600mA 1011: 650mA 1110: 700mA 1111: 850mA       |

| Naı   | ne    | Function              | Addr        | Reset                                                                                                                                                                                                 |

|-------|-------|-----------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|