## Configurable, Isolated 10-bit ADCs for Multi-Range Binary Inputs

#### **General Description**

The MAX14001/MAX14002 are isolated, single-channel analog-to-digital converters (ADCs) with programmable voltage comparators and inrush current control optimized for configurable binary input applications. 3.75kV<sub>RMS</sub> of integrated isolation is provided between the binary input side (field-side) and the comparator output/SPI-side (logic-side) of the MAX14001/MAX14002. An integrated, isolated, DC-DC converter powers all field-side circuitry, and this allows running field-side diagnostics even when no input signal is present. The 20-pin SSOP package provides 5.5mm of creepage and clearance with group II CTI rating.

These devices continually digitize the input voltage on the field-side of an isolation barrier and transmit the data across the isolation barrier to the logic-side of the device where the magnitude of the input voltage is compared to programmable thresholds. The binary comparator output pin is high when the input voltage is above the upper threshold and low when it is below the lower threshold. Response time of the comparator to an input change is less than 150µs with filtering disabled. With filtering enabled, the comparator uses the moving average of the last 2, 4, or 8 ADC readings. Both filtered and unfiltered ADC readings are available through the 5MHz SPI port, which is also used to set comparator thresholds and other device configuration.

The MAX14001/MAX14002 control the current of a binary input through an external, high-voltage FET. This current cleans relay contacts and attenuates input noise. An inrush comparator monitoring the ADC readings triggers the inrush current, or wetting pulse. The inrush trigger threshold, current magnitude, and current duration are all programmable in the MAX14001 but are fixed in the MAX14002. When the high-voltage FET is not providing inrush current, it switches to bias mode. Bias mode places a small current load on the binary input to attenuate capacitively coupled noise. The level of bias current is programmable between 50µA and 3.75mA in both the MAX14001 and MAX14002. This allows optimization of the tradeoff between noise attenuation and power dissipation.

#### **Benefits and Features**

- Enables Robust Detection of Binary Inputs

- Programmable Input Bias Current Rejects Line Noise

- · 3.75kV<sub>RMS</sub> of Isolation for 60 Seconds

- 5.5mm of Creepage and Clearance

- · Group II CTI Package Material

- Reduces BOM and Board Space Through High Integration

- 10-bit, 10ksps ADC

- · Binary Threshold Comparators

- · Control Circuit for Driving a Depletion Mode FET

- · Isolation for Both Data and DC-DC Supply

- · 20-SSOP Package

- Increases Equipment "Up Time" and Simplifies System Maintenance

- · Enables Field-Side Diagnostics

- · Automatic Self-Diagnostics

- Provides Unparalleled Flexibility

- · Programmable Upper and Lower Input Thresholds

- Programmable Inrush Current Activation Threshold, Magnitude, and Duration

- · Daisy-Chainable SPI Interface

#### **Applications**

- High-Voltage Binary Input (12V-300V)

- Distribution Automation

- Substation Automation

- Industrial Control, Multi-Range, Digital Input Modules with Individually Isolated Inputs

### **Safety Regulatory Approvals (Pending)**

• UL According to UL1577

Ordering Information appears at end of data sheet.

## Configurable, Isolated 10-bit ADCs for Multi-Range Binary Inputs

### **Absolute Maximum Ratings**

| V <sub>DDL</sub> to GNDL0.3V                      | / to +6V | V <sub>DDF</sub> to GNDF                                              | 0.3V to +6V    |

|---------------------------------------------------|----------|-----------------------------------------------------------------------|----------------|

| V <sub>DD</sub> to GNDL0.3V                       |          | Short-Circuit Duration (FAULT, COUT, SDO to GNDL or V <sub>DD</sub> ) | Continuous     |

|                                                   |          | Continuous Power Dissipation ( $T_A = +70^{\circ}$ C)                 | Continuous     |

| Logic-Side Outputs (SDO, COUT)                    |          | 20-pin SSOP                                                           | 952.4mW        |

| to GNDL0.3V to (V <sub>DDL</sub>                  | + 0.3V)  | Operating Temperature Range                                           |                |

| V <sub>REFIN</sub> , V <sub>AIN</sub> to AGND0.3V | / to +2V | Junction Temperature                                                  | +150°C         |

| AGND to GNDF0.3V to                               | o +0.3V  | Storage Temperature Range                                             | 65°C to +150°C |

| GATE to GNDF0.3V                                  | / to +4V | Lead Temperature (soldering, 10s)                                     | +300°C         |

| IFET to GNDF0.3V t                                | to +12V  | Soldering Temperature (reflow)                                        | +260°C         |

| ISET to GNDF0.3V                                  | / to +2V |                                                                       |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Thermal Characteristics (Note 1)**

20-pin SSOP

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ).......84°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ).......32°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **Electrical Characteristics**

$(V_{DDL}-V_{GNDL}=1.71V~to~5.5V,~V_{DD}-V_{GNDL}=3.0V~to~3.6V,~R_{|SET}=120k\Omega,~T_{A}=-40^{\circ}C~to~+125^{\circ}C,~V_{GNDF}=V_{GNDL}.~Typical~values~are~at~T_{A}=+25^{\circ}C~with~V_{DDL}=V_{DD}=+3.3V,~R_{|SET}=120k\Omega,~V_{GNDF}=V_{GNDL}.)~(Notes~2,~3)$

| PARAMETER                                    | SYMBOL               | CONDITIONS                                            | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------------|----------------------|-------------------------------------------------------|------|------|------|-------|

| POWER SUPPLIES                               |                      |                                                       |      |      |      |       |

| Logic Power Supply                           | V <sub>DDL</sub>     |                                                       | 1.71 |      | 5.5  | V     |

| Logic Supply Current                         | I <sub>DDL</sub>     | $V_{DDL}$ = 3.3V, no load, $\overline{CS}$ = high     |      | 0.7  | 1.5  | mA    |

| Isolated DC-DC Power Supply Input Voltage    | V <sub>DD</sub>      |                                                       | 3.0  | 3.3  | 3.6  | V     |

| Isolated DC-DC Supply Input Current          | I <sub>DD</sub>      | V <sub>DD</sub> = 3.3V                                |      | 4.8  | 8    | mA    |

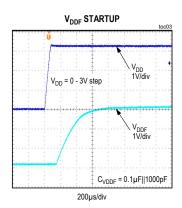

| Logic Power-Up Delay                         |                      |                                                       |      |      | 0.2  | ms    |

| Field Power-Up Delay                         |                      | C <sub>VDDF</sub> = 0.1µF                             |      |      | 1    | ms    |

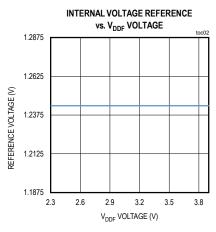

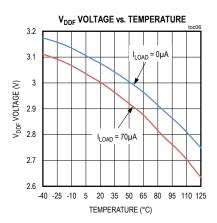

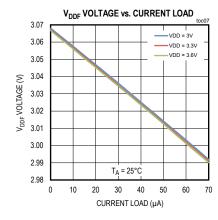

| Field Power Supply                           | $V_{DDF}$            | C <sub>VDDF</sub> = 0.1µF, unregulated output voltage | 2.5  | 3.0  | 3.5  | V     |

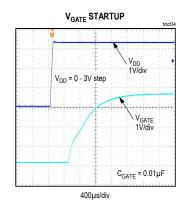

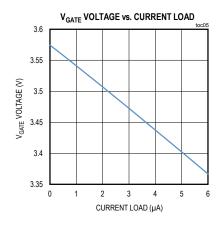

| Gate Charge Pump<br>Voltage                  | V <sub>GATE</sub>    | 1μA pull-down                                         | 3    | 3.6  | 4    | V     |

| Logic-Side Undervoltage                      | V <sub>UVLOL</sub>   | V <sub>DD</sub> ≥ 3V                                  | 1.5  | 1.6  | 1.66 | V     |

| Lockout Threshold                            | V <sub>UVLOD</sub>   | V <sub>DDL</sub> ≥ 1.71V                              | 2.69 | 2.82 | 2.95 | V     |

| Logic-Side Undervoltage<br>Lockout Threshold | V <sub>UVLHYST</sub> |                                                       |      | 50   |      | mV    |

| Hysteresis                                   | V <sub>UVDHYST</sub> |                                                       |      | 100  |      | mV    |

| Field-Side Undervoltage<br>Lockout Threshold | V <sub>UVLOF</sub>   | (Note 4)                                              | 1.95 | 2.1  | 2.25 | V     |

### **Electrical Characteristics (continued)**

$(V_{DDL}-V_{GNDL}=1.71V~to~5.5V,~V_{DD}-V_{GNDL}=3.0V~to~3.6V,~R_{ISET}=120k\Omega,~T_{A}=-40^{\circ}C~to~+125^{\circ}C,~V_{GNDF}=V_{GNDL}.~Typical~values~are~at~T_{A}=+25^{\circ}C~with~V_{DDL}=V_{DD}=+3.3V,~R_{ISET}=120k\Omega,~V_{GNDF}=V_{GNDL}.)~(Notes~2,~3)$

| PARAMETER                                                  | SYMBOL               | CONDITIONS                                                                           | MIN   | TYP  | MAX                          | UNITS  |

|------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------|-------|------|------------------------------|--------|

| Field-Side Undervoltage<br>Lockout Threshold<br>Hysteresis | V <sub>UVFHYST</sub> |                                                                                      |       | 100  |                              | mV     |

| PROTECTION                                                 |                      |                                                                                      | •     |      |                              |        |

| ESD                                                        |                      | Any pin to GNDL or GNDF inclusive                                                    |       | ±2   |                              | kV     |

| EFT (Burst)                                                |                      | System-level requirement IEC 61000-4-4 common mode (Note 5)                          |       | 3    |                              | kV     |

| DYNAMIC                                                    |                      |                                                                                      |       |      |                              |        |

| Common-Mode Transient<br>Immunity                          | СМТІ                 | (Note 6)                                                                             |       | 50   |                              | kV/μs  |

| ADC AND COMPARATOR                                         | 1                    |                                                                                      |       |      |                              |        |

| Input Voltage Range                                        | V <sub>AIN</sub>     | Nominal measurement range                                                            | 0     |      | V <sub>REFIN</sub><br>(1.25) | V      |

| Reference Input Range                                      | V <sub>REFIN</sub>   |                                                                                      | 1.15  | 1.25 | 1.35                         | V      |

| ADC Resolution                                             |                      |                                                                                      | 10    |      |                              | Bits   |

| Gain Error                                                 | GE                   | V <sub>IN</sub> = 98% V <sub>REF</sub> , excluding offset error and reference errors | -0.55 |      | +0.55                        | %      |

| Offset Error                                               | OE                   | V <sub>IN</sub> = 2% V <sub>REF</sub> , offset calculated                            | -0.2  |      | +0.2                         | %FS    |

| Differential Nonlinearity                                  | DNL                  |                                                                                      |       |      | ±1                           | LSB    |

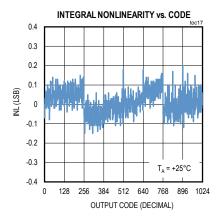

| Integral Nonlinearity                                      | INL                  | Included in the gain + offset window                                                 |       |      | ±1                           | LSB    |

| Input Leakage Current                                      | IILR                 | V <sub>AIN</sub> = 1.25V                                                             | -200  |      | +200                         | nA     |

| Throughput                                                 |                      |                                                                                      | 8     | 10   | 12                           | ksps   |

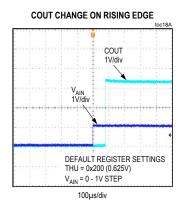

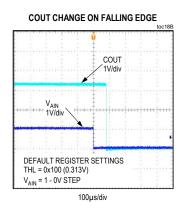

| Latency (No Filtering)                                     |                      | AIN step input to COUT transition (Notes 4, 7)                                       | 12    |      | 150                          | μs     |

| Latency (2 Readings)                                       |                      | AIN step input to COUT transition (Notes 4, 7)                                       | 92    |      | 270                          | μs     |

| Latency (4 Readings)                                       |                      | AIN step input to COUT transition (Notes 4, 7)                                       | 180   |      | 510                          | μs     |

| Latency (8 Readings)                                       |                      | AIN step input to COUT transition (Notes 4, 7)                                       | 340   |      | 990                          | μs     |

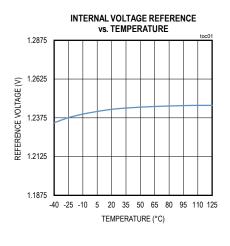

| INTERNAL VOLTAGE REI                                       | FERENCE              |                                                                                      |       |      |                              |        |

| Nominal Output Voltage                                     |                      |                                                                                      |       | 1.25 |                              | V      |

| Output Voltage Accuracy                                    |                      | Over the entire temperature range                                                    | -5    |      | +5                           | %      |

| Output Voltage<br>Temperature Drift                        | T <sub>CVOUT</sub>   |                                                                                      |       | 50   |                              | ppm/°C |

| EXTERNAL VOLTAGE RE                                        | FERENCE              |                                                                                      |       |      |                              |        |

| Reference Voltage                                          |                      |                                                                                      | 1.15  | 1.25 | 1.35                         | V      |

| Available Bias Current                                     |                      | When powered from V <sub>DDF</sub> (series) or REFIN (shunt)                         | 70    |      |                              | μΑ     |

### **Electrical Characteristics (continued)**

$(V_{DDL}-V_{GNDL}=1.71V~to~5.5V,~V_{DD}-V_{GNDL}=3.0V~to~3.6V,~R_{|SET}=120k\Omega,~T_{A}=-40^{\circ}C~to~+125^{\circ}C,~V_{GNDF}=V_{GNDL}.~Typical~values~are~at~T_{A}=+25^{\circ}C~with~V_{DDL}=V_{DD}=+3.3V,~R_{|SET}=120k\Omega,~V_{GNDF}=V_{GNDL}.)~(Notes~2,~3)$

| PARAMETER              | SYMBOL            | CONDITIONS                                                           | MIN                   | TYP                        | MAX                   | UNITS |

|------------------------|-------------------|----------------------------------------------------------------------|-----------------------|----------------------------|-----------------------|-------|

| BIAS CURRENT DAC       | •                 |                                                                      | •                     |                            |                       |       |

| Full-Scale Current     |                   | Excludes R <sub>ISET</sub> errors                                    | 3.375                 | 3.75                       | 4.125                 | mA    |

| Resolution             |                   |                                                                      |                       | 0.25                       |                       | mA    |

| Offset Error           |                   | IBIAS[3:0] = 0 (see CFG register)                                    |                       | 50                         | 100                   | μA    |

| Integral Nonlinearity  | INL               |                                                                      |                       | 0.25                       |                       | LSB   |

| INRUSH CURRENT DAG     | ;                 |                                                                      |                       |                            |                       |       |

| Full-Scale Current     |                   | Excludes R <sub>ISET</sub> errors                                    | 94.5                  | 105                        | 115.5                 | mA    |

| Resolution             |                   |                                                                      |                       | 7                          |                       | mA    |

| Offset                 |                   | IINR[3:0] = 0 (see INRP register)                                    |                       | 50                         | 100                   | μA    |

| Integral Nonlinearity  | INL               |                                                                      |                       | 0.25                       |                       | LSB   |

| Inrush Current         |                   | MAX14002 only. Excludes R <sub>ISET</sub> errors                     | 44.1                  | 49                         | 53.9                  | mA    |

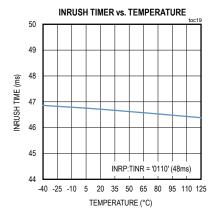

| INRUSH TIMER           | '                 |                                                                      |                       |                            |                       |       |

| Range                  |                   | Nominal                                                              | 0                     |                            | 120                   | ms    |

| Resolution             |                   | Programmed by TINR[3:0] (see INRP register)                          |                       | 8                          |                       | ms    |

| Error                  |                   |                                                                      | -20                   |                            | +20                   | %     |

|                        |                   | DU1 = 0, DU0 = 1 (see INRP register)                                 |                       | 1.6                        |                       |       |

| Maximum Duty Cycle     |                   | DU1 = 1, DU0 = 0 (see INRP register)                                 |                       | 3.1                        |                       | %     |

|                        |                   | DU1 = 1, DU0 = 1 (see INRP register)                                 |                       | 6.3                        |                       |       |

| Inrush Duration        |                   | MAX14002 only                                                        | 38.4                  | 48                         | 57.6                  | ms    |

| INRUSH COMPARATOR      |                   |                                                                      |                       |                            |                       |       |

| Range                  |                   |                                                                      | 0                     |                            | ADC FS                | V     |

| Resolution             |                   |                                                                      | 10                    |                            |                       | Bits  |

| Latency (No Filtering) |                   | From input voltage = INRT until IINR = 50% of set value (Notes 4, 7) | 22                    |                            | 160                   | μs    |

| Latency (2 Readings)   |                   | From input voltage = INRT until IINR = 50% of set value (Notes 4, 7) | 102                   |                            | 280                   | μs    |

| Latency (4 Readings)   |                   | From input voltage = INRT until IINR = 50% of set value (Notes 4, 7) | 192                   |                            | 520                   | μs    |

| Latency (8 Readings)   |                   | From input voltage = INRT until IINR = 50% of set value (Notes 4, 7) | 356                   |                            | 1000                  | μs    |

| LOGIC I/O LEVELS       | •                 |                                                                      |                       |                            |                       |       |

| Input High Voltage     | V <sub>IH</sub>   | SCLK, SDI, $\overline{\text{CS}}$                                    | 0.7 x V <sub>DD</sub> | )L                         |                       | V     |

| Input Low Voltage      | V <sub>IL</sub>   | SCLK, SDI, CS                                                        |                       |                            | .3 x V <sub>DDL</sub> | V     |

| Input Hysteresis       | V <sub>HYST</sub> | SCLK, SDI, CS                                                        |                       | 0.05 x<br>V <sub>DDL</sub> |                       | V     |

#### **Electrical Characteristics (continued)**

$(V_{DDL}-V_{GNDL}=1.71V~to~5.5V,~V_{DD}-V_{GNDL}=3.0V~to~3.6V,~R_{|SET}=120k\Omega,~T_{A}=-40^{\circ}C~to~+125^{\circ}C,~V_{GNDF}=V_{GNDL}.~Typical~values~are~at~T_{A}=+25^{\circ}C~with~V_{DDL}=V_{DD}=+3.3V,~R_{|SET}=120k\Omega,~V_{GNDF}=V_{GNDL}.)~(Notes~2,~3)$

| PARAMETER                                              | SYMBOL                 | CONDITIONS                                                               | MIN                   | TYP | MAX | UNITS |

|--------------------------------------------------------|------------------------|--------------------------------------------------------------------------|-----------------------|-----|-----|-------|

| Output High Voltage                                    | V <sub>OH</sub>        | SDO, COUT, sourcing 4mA                                                  | V <sub>DDL</sub> - 0. | 4   |     | V     |

| Output Low Voltage                                     | V <sub>OL</sub>        | SDO, COUT, FAULT, sinking 4mA                                            |                       |     | 0.4 | V     |

| Output High-Impedance<br>Leakage Current               | l <sub>OL</sub>        | SDO, FAULT                                                               | -1                    |     | +1  | μA    |

| Input Leakage Current                                  | I <sub>IL</sub>        | SCLK, SDI, CS                                                            | -1                    |     | +1  | μA    |

| Input Capacitance                                      | C <sub>IN</sub>        | SCLK, SDI, <del>CS</del> , f = 1MHz                                      |                       | 2   |     | pF    |

| SPI TIMING CHARACTER                                   | RISTICS                |                                                                          |                       |     |     |       |

| SCLK Clock Frequency                                   | f <sub>SCLK</sub>      | Single device                                                            |                       |     | 5   | MHz   |

| SCLK Clock Period                                      | tsclk                  | Single device                                                            | 200                   |     |     | ns    |

| SCLK Pulse-Width High                                  | tsclkh                 | Single device                                                            | 80                    |     |     | ns    |

| SCLK Pulse-Width Low                                   | t <sub>SCLKL</sub>     | Single device                                                            | 80                    |     |     | ns    |

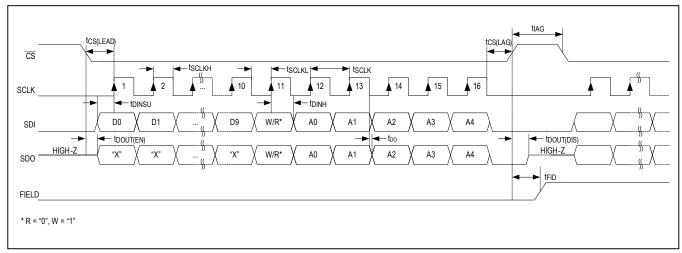

| CS Fall-to-SCLK Rise Time                              | t <sub>CS(lead)</sub>  |                                                                          | 80                    |     |     | ns    |

| SCLK Fall-to-CS Rise Time                              | t <sub>CS(lag)</sub>   |                                                                          | 80                    |     |     | ns    |

| SDI Hold Time                                          | t <sub>DINH</sub>      |                                                                          | 40                    |     |     | ns    |

| SDI Setup Time                                         | t <sub>DINSU</sub>     |                                                                          | 40                    |     |     | ns    |

| SDO Enable Time (CS Falling to SDO Valid)              | t <sub>DOUT(en)</sub>  | C <sub>L</sub> = 50pF                                                    | 40                    |     |     | ns    |

| SDO Disable Time (CS<br>Rising to SDO Three-<br>State) | t <sub>DOUT(dis)</sub> | C <sub>L</sub> = 50pF                                                    | 40                    |     |     | ns    |

| Output Data Propagation Delay                          | t <sub>DO</sub>        | C <sub>L</sub> = 50pF. SCLK falling-edge to SDO valid                    |                       |     | 50  | ns    |

| Write-Command to Field Implementation Delay            | t <sub>FID</sub>       | From CS de-assertion until field-side registers are loaded               |                       |     | 165 | ns    |

| Inter-Access Gap                                       | t <sub>IAG</sub>       | Minimum time $\overline{\text{CS}}$ must be de-asserted between commands | 920                   |     |     | ns    |

- Note 2: All devices are 100% production tested at  $T_A$  = +25°C. Specifications for all temperature limits are guaranteed by design.

- **Note 3:** All currents into the device are positive; all currents out of the device are negative. All voltages are referenced to their respective ground (GNDL or GNDF), unless otherwise noted.

- Note 4: Guaranteed by characterization; not production tested.

- Note 5: EFT voltage according to IEC 61004-4 is tested through direct coupling to the generator.

- Note 6: CMTI is the maximum sustainable common-mode voltage slew rate while maintaining the correct output states. CMTI applies to both rising and falling common-mode voltage edges. Tested with the transient generator connected between GNDF and GNDL (V<sub>CM</sub> = 1000V).

- Note 7: Latency numbers are based on the following condition: a full-scale step is applied at the ADC input and THU is set to mid-scale value (0x1ff). Latency is the delay from the step at the ADC input to the digital comparator output.

#### **Insulation Characteristics**

| PARAMETER                                 | SYMBOL            | CONDITIONS                                                              | VALUE     | UNITS             |

|-------------------------------------------|-------------------|-------------------------------------------------------------------------|-----------|-------------------|

| Partial Discharge Test<br>Voltage         | V <sub>PR</sub>   | Method B1 = V <sub>IORM</sub> x 1.875 (t = 1s, partial discharge < 5pC) | 1050      | V <sub>P</sub>    |

| Maximum Repetitive Peak Isolation Voltage | V <sub>IORM</sub> | (Note 8)                                                                | 560       | V <sub>P</sub>    |

| Maximum Working Isolation Voltage         | V <sub>IOWM</sub> | Continuous RMS voltage (Note 8)                                         | 400       | V <sub>RMS</sub>  |

| Maximum Transient Isolation Voltage       | V <sub>IOTM</sub> | t = 1s                                                                  | 6300      | V <sub>P</sub>    |

| Maximum Withstand<br>Isolation Voltage    | V <sub>ISO</sub>  | t = 60s, f = 60Hz (Notes 8, 9)                                          | 3.75      | kV <sub>RMS</sub> |

| Maximum Surge Isolation Voltage           | V <sub>IOSM</sub> | Basic Insulation, 1.2/50µs surge pulse per IEC 61000-4-5                | 7.5       | kV                |

| Insulation Resistance<br>Logic-to-Field   | R <sub>S</sub>    | T <sub>A</sub> = +125°C, V <sub>IO</sub> = 500V                         | >109      | Ω                 |

| Barrier Capacitance<br>Logic-to-Field     | CIO               | f = 1MHz (Note 10)                                                      | 10        | pF                |

| Minimum Creepage<br>Distance              | CPG               | SSOP                                                                    | 5.5       | mm                |

| Minimum Clearance<br>Distance             | CLR               | SSOP                                                                    | 5.5       | mm                |

| Internal Clearance                        |                   | Distance through insulation                                             | 0.015     | mm                |

| Comparative Tracking<br>Resistance Index  | СТІ               | Material Group II (IEC 60112)                                           | >400      |                   |

| Climatic Category                         |                   |                                                                         | 40/125/21 |                   |

| Pollution Degree (DIN VDE 0110, Table 1)  |                   |                                                                         | 2         |                   |

Note 8:  $V_{ISO}$ ,  $V_{IOWM}$  and  $V_{IORM}$  are defined by the IEC 60747-5-5 standard.

Note 9: Product is qualified  $V_{ISO}$  for 60 seconds. 100% production tested at 120% of  $V_{ISO}$  for 1s.

Note 10: Capacitance is measured with all pins on field-side and logic-side tied together.

### **Safety Regulatory Approvals (Pending)**

#### UL

The MAX14001/MAX14002 are certified under UL1577.

Rated up to  $3750\mbox{V}_{\mbox{RMS}}$  isolation voltage for basic insulation.

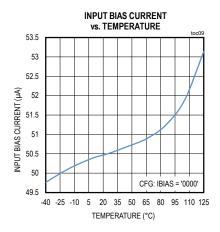

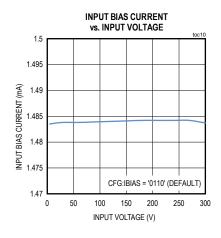

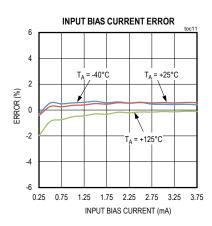

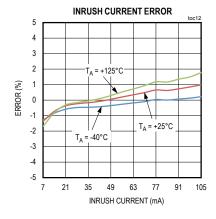

### **Typical Operating Characteristics**

$(V_{DDL} = V_{DD} = +3.3V, R_{ISET} = 120k\Omega, isolated GNDF and GNDL, high-voltage FET is IXTY08N100D2, with T_A = +25°C unless otherwise noted.)$

### **Typical Operating Characteristics (continued)**

$(V_{DDL} = V_{DD} = +3.3V, R_{ISET} = 120k\Omega$ , isolated GNDF and GNDL, high-voltage FET is IXTY08N100D2, with  $T_A = +25^{\circ}C$  unless otherwise noted.)

### **Typical Operating Characteristics (continued)**

$(V_{DDL} = V_{DD} = +3.3V, R_{ISET} = 120k\Omega, isolated GNDF and GNDL, high-voltage FET is IXTY08N100D2, with T_A = +25°C unless otherwise noted.)$

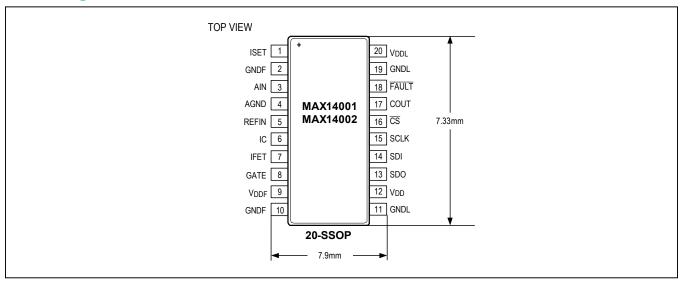

## **Pin Configuration**

### **Pin Description**

|          |                  |           | - Investory                                                                                                                                                                                                               |

|----------|------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN      | NAME             | REFERENCE | FUNCTION                                                                                                                                                                                                                  |

| POWER SU | IPPLY            |           |                                                                                                                                                                                                                           |

| 20       | V <sub>DDL</sub> | GNDL      | Power Input for the Logic-Side of the MAX14001/MAX14002. Bypass with 10μF  1000pF capacitors to GNDL.                                                                                                                     |

| 12       | V <sub>DD</sub>  | GNDL      | Power Input for the Isolated DC-DC Converter. The DC-DC converter powers the field-side of the MAX14001/MAX14002. Bypass with 10µF  1000pF capacitors to GNDL.                                                            |

| 11, 19   | GNDL             | _         | Power and Signal Ground for All Logic-Side Pins.                                                                                                                                                                          |

| 9        | V <sub>DDF</sub> | GNDF      | Unregulated Output of the DC-DC Converter. Bypass to GNDF with 0.1µF  1000pF capacitors. The 1000pF capacitor should be placed as close to the pin as possible.                                                           |

| 8        | GATE             | GNDF      | Bias Voltage for the Gate of the External Depletion Mode FET. Connect a 0.01µF capacitor from GATE to GNDF.                                                                                                               |

| 2, 10    | GNDF             | _         | Field-side ground for everything except the ADC front-end and voltage reference.                                                                                                                                          |

| ANALOG   |                  |           |                                                                                                                                                                                                                           |

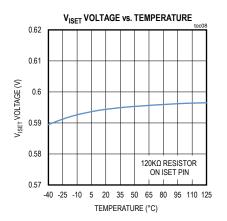

| 1        | ISET             | GNDF      | Connect a $120k\Omega$ Resistor From ISET to GNDF. This generates a reference current used to establish the correct bias and inrush currents. Parasitic capacitance on this pin should not exceed 10pF.                   |

| 7        | IFET             | GNDF      | Current Sink Input for Inrush and Bias Current. This pin is buffered from high voltage by connecting it to the source of the external high-voltage FET. Connect a 1000pF capacitor from IFET to GNDF.                     |

| 3        | AIN              | AGND      | Analog Input. The ADC measures the voltage on this pin with respect to AGND.                                                                                                                                              |

| 4        | AGND             | _         | Analog Ground Reference for AIN and REFIN                                                                                                                                                                                 |

| 5        | REFIN            | AGND      | Optional External Voltage Reference Input (Nominally 1.25V). When an external reference is used, connect a 0.1µF bypass capacitor from REFIN to AGND. When an internal reference is used, connect REFIN directly to AGND. |

| 6        | IC               | GNDF      | Internally Connected. Connect to GNDF.                                                                                                                                                                                    |

## **Pin Description (continued)**

| PIN     | NAME  | REFERENCE | FUNCTION                                                                                                                                                                                                                     |

|---------|-------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIGITAL |       |           |                                                                                                                                                                                                                              |

| 18      | FAULT | GNDL      | Open-Drain Output That Asserts Low During a Number of Different Error Conditions. The cause of the error is latched in the FLAGS register. See <i>Diagnostic and Fault Reporting Features</i> for details on clearing FAULT. |

| 17      | COUT  | GNDL      | Digital Comparator Output. COUT is high when AIN is above the upper threshold (THU) and low when AIN is below the lower threshold (THL).                                                                                     |

| 16      | CS    | GNDL      | Chip Select for SPI Interface. Assert low to enable SPI functions and SDO. SDO is high impedance when $\overline{\text{CS}}$ is high.                                                                                        |

| 15      | SCLK  | GNDL      | Serial Clock for SPI Interface                                                                                                                                                                                               |

| 14      | SDI   | GNDL      | Serial Data Input for SPI Interface (MOSI)                                                                                                                                                                                   |

| 13      | SDO   | GNDL      | Serial Data Out for SPI Interface (MISO)                                                                                                                                                                                     |

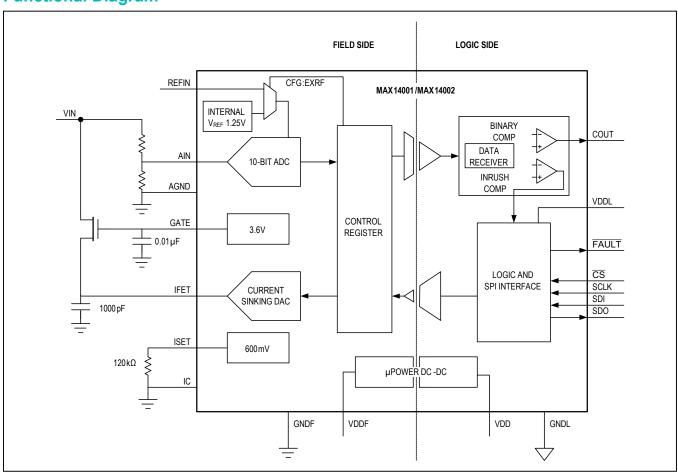

## **Functional Diagram**

#### **Detailed Description**

The MAX14001/MAX14002 are 10-bit ADCs with a 3.75kV<sub>RMS</sub> isolated SPI interface. Additional features include a programmable magnitude comparator, programmable inrush current for cleaning relay contacts, and programmable input bias current to optimize power dissipation while reducing capacitively coupled input noise. The ADC and all field-side circuits are powered by an integrated, isolated, DC-DC converter that allows field-side functionality to be verified even when there is no input signal or other field-side supply. This makes the MAX14001/MAX14002 ideally suited for high density, multi-range, individually isolated, binary input modules.

#### **ADC**

The devices' ADC employs a 10-bit SAR architecture with a nominal sampling rate of 10ksps, and has an input voltage range of 0V to +1.25V with respect to AGND. After power-up, the ADC runs continually at the nominal sampling rate. The 10-bit unfiltered ADC reading and filtered ADC reading are both available via the SPI interface. Filtering averages the most recent 2, 4, or 8 readings depending on the value of the FT[1:0] bits in the CFG register. A binary comparator responds within 150µs to changes in input

voltage by continually comparing the latest ADC reading to the programmed thresholds (refer to the EC table for response times when using the ADC filter). When the latest ADC reading is higher than the upper threshold (THU), the comparator's output pin (COUT) is high and when it is lower than the lower threshold (THL), the comparator's output pin (COUT) is low.

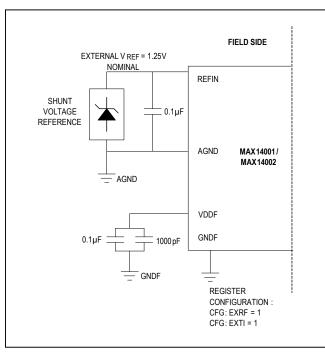

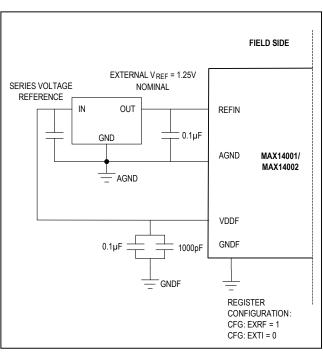

#### Internal/External Voltage Reference Configuration

The MAX14001/MAX14002 feature both internal and external voltage reference capability. The 1.25V internal reference has a maximum error of  $\pm 5\%$  over the entire operating temperature range. If higher accuracy is required, an external reference may be used. The external reference may be either series or shunt, but must not draw more than  $70\mu A$  of supply current. Series references must be powered from  $V_{DDF}$  while shunt references are powered from an internal  $70\mu A$  current source that is connected to the REFIN pin. Internal/external voltage reference mode is selected using the SPI interface to program the CFG register. Refer to Table 1 for the CFG register configuration, Figure 1 for shunt reference hardware connection, and Figure 2 for series reference hardware connection.

Figure 1. Shunt Voltage Reference Connection

Figure 2. Series Voltage Reference Connection

| REFERENCE CONFIGURATION   | CFG:EXRF | CFG:EXTI | CONNECTION                                                                                                                              |

|---------------------------|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Internal Reference        | 0        | 0        | Connect REFIN directly to AGND.                                                                                                         |

| External Series Reference | 1        | 0        | Series reference is supplied by $V_{DDF}$ . Output is connected to the REFIN pin. Bypass REFIN to AGND with a $0.1\mu F$ capacitor.     |

| External Shunt Reference  | 1        | 1        | Internal current source is turned on. Shunt reference is connected between REFIN and AGND. Bypass REFIN to AGND with a 0.1µF capacitor. |

**Table 1. Voltage Reference Register Configuration**

#### **ADC Error**

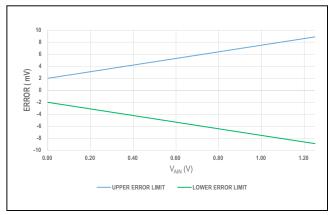

The uncalibrated error of the ADC lies within the window shown in the Figure 3 ADC Error Window. The boundaries of the box are defined by the offset and gain error from the EC table and include INL errors as well as drift over temperature. The upper-boundary is set by the most positive offset combined with the most positive gain error. Conversely, the lower-boundary is set by the most negative offset combined with the most negative gain error.

$$ERROR_{MAX} = OE \times FS + V_{IN} \times GE$$

Where OE is the offset error in %FS, FS is the full scale voltage,  $V_{\mbox{\scriptsize IN}}$  is the input voltage being measured, and GE is the gain error in %.

If a resistor-divider is used in front of the ADC, FS and  $V_{\text{IN}}$  can be the voltages at the input of the divider. For total system error, the resistive-divider error and the error of the voltage reference in percent are added to the gain error of the ADC.

SYSTEM ERROR<sub>MAX</sub> =

$$OE \times FS + V_{IN} \times (GE + ERROR_R + ERROR_{VRFF})$$

Where OE is the offset error in %FS, FS is the full scale voltage,  $V_{IN}$  is the input voltage being measured, GE is the gain error in %, ERROR<sub>R</sub> is the resistive-divider error in %, and ERROR<sub>VRFF</sub> is the voltage reference error in %.

For example, assume:

- All errors specs are symmetrical.

- |Maximum Positive Error| = |Maximum Negative Errorl

- The input resistive-divider is made of 1% resistors and divides the binary voltage by a nominal factor of 240.

- Maximum resistive-divider error ERROR<sub>R</sub> = 2%

Figure 3. ADC Error Window (Excludes V<sub>RFF</sub> Error)

- A nominal 1.25V reference with an error of 5%

- Full-scale input voltage  $F_S = 1.25V \times 240 = 300$

- ERROR<sub>VRFF</sub> = 5%

- ADC offset error OE = 0.3%

- ADC gain error GE = 0.3%

- Input voltage V<sub>IN</sub> = 200V

SYSTEM ERROR<sub>MAX</sub> =

$$0.3\% \times 300V + V_{IN} \times (0.3\% + 2\% + 5\%)$$

When  $V_{IN}$  = 200V, the maximum error is 15.5V.

If the comparator threshold is set at 200V (ADC reading of decimal 682), the comparator could trip with a voltage as low as 184.5V or as high as 215.5V. Conversely, if the ADC is to read 682, the nominal input voltage would be 200V, but the actual voltage could be as high a 215.5V or as low as 184.5V.

## Configurable, Isolated 10-bit ADCs for Multi-Range Binary Inputs

#### **High-Voltage FET Current Control**

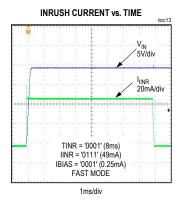

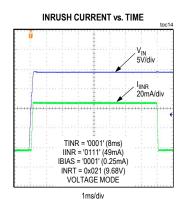

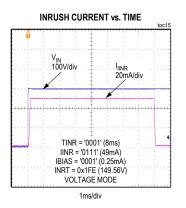

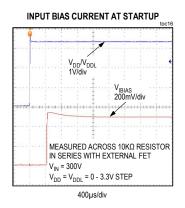

The devices control a high-voltage depletion mode FET that can be used to sink inrush current for cleaning relay contacts while contacts are closing, or a smaller bias current for input noise suppression while contacts are open. When the inrush pulse is finished, the FET current is reduced to the bias level, lowering power dissipation in the FET while still providing an input load. Inrush current is fixed in the MAX14002 (49mA for 48ms) but is configurable in the MAX14001. The MAX14001's inrush current magnitude and duration are both programmable: the magnitude ranges from 50µA to 105mA in 7mA increments, and the duration ranges from 0ms to 120ms in 8ms increments. Bias current is adjustable in both the MAX14001 and MAX14002, and ranges from 50uA to 3.75mA in 0.25mA increments.

The MAX14001's inrush pulse can be initiated in one of two ways: voltage triggered inrush mode based on the ADC reading or FAST inrush mode based on the highvoltage FET current level. In voltage triggered inrush mode (FAST bit in the CFG register = 0), the pulse is initiated when the ADC reading equals or exceeds the programmed trigger threshold in the INRT register. Once an inrush pulse has been triggered, the ADC reading must drop below the re-arm threshold in the INRR register before another inrush pulse can be triggered. In FAST mode (FAST bit in the CFG register = 1), the inrush pulse starts as soon as the input signal is able to supply the inrush current. Re-arming occurs when the input no longer supplies enough current to the high-voltage FET (either inrush or bias current depending on the present mode). The MAX14002 operates in FAST mode only.

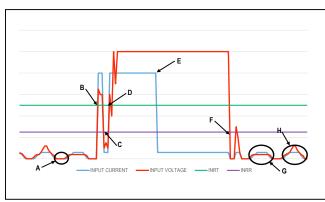

Figure 4. Voltage Triggered Inrush Mode

Figure 4 and Figure 5 illustrate the two methods for triggering a pulse of inrush current.

#### **Voltage Mode**

- A) The high-voltage FET is trying to sink bias current, but cannot because the input signal is not supplying enough current.

- B) When the input voltage increases to the inrush trigger threshold (INRT), the FET current is increased to the inrush level and the inrush timer is started.

- C) Contact bounce causes the input voltage to drop below the inrush reset threshold (INRR). The FET current is reduced to the bias level and the inrush timer is reset.

- D) The input voltage again rises to the inrush trigger threshold. The FET current is increased to the inrush level and the inrush timer is started.

- E) The inrush timer expires and the FET current is reduced to the bias level.

- F) The input voltage drops below the inrush re-arm threshold (INRR). The inrush timer is reset and prepared to deliver the next inrush pulse. The FET current remains at the bias level.

- G) The noise pulse is fully clamped at the turn-on voltage of the FET circuit.

- H) Higher energy noise pulse that is partially clamped by the bias current. Noise current exceeds the bias current so the voltage rises above the turn-on voltage of the FET circuit.

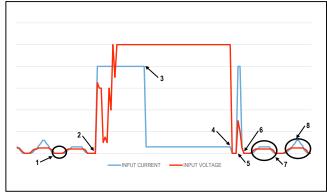

Figure 5. FAST Inrush Mode

## Configurable, Isolated 10-bit ADCs for Multi-Range Binary Inputs

#### **FAST Mode**

- The high-voltage FET is trying to sink the inrush current, but cannot because the input signal is not supplying enough current. Since the current level cannot be met, the FET current is set to the inrush level, and the inrush timer is reset.

- 2) The input voltage increases and supplies enough current for the inrush pulse. The inrush timer is started.

- The inrush timer expires and the FET current is reduced to the bias level.

- 4) The input voltage drops and can no longer supply the bias current. The inrush timer is reset and the FET current is set to the inrush level.

- Contact bounce raises the input voltage and supplies enough current for an inrush pulse. The inrush timer is started.

- 6) The input voltage drops and can no longer supply the inrush current. The inrush timer is reset and the FET current remains the inrush level.

- 7) The noise pulse is fully clamped at the turn-on voltage of the FET circuit.

- 8) Higher energy noise pulse is fully clamped by the inrush current. Noise current exceeds the bias current, but since the FET is trying to sink the larger input current, the input current rises and the voltage remains clamped at the turn-on voltage of the FET circuit.

#### Repetitive Inrush Pulse Limiting (MAX14001 Only)

The MAX14001 can limit repetitive inrush pulses to prevent overheating from abnormal input signals that would otherwise trigger a continuous stream of inrush pulses. When the pulse limiting function is enabled, the MAX14001 monitors the percentage of time that the inrush current is flowing. When it exceeds the duty cycle threshold over the last 10 seconds, additional inrush pulses are disabled for the next 10 seconds. When the pulse limiting is triggered, the INRD bit in the FLAGS register is set and FAULT is asserted if the EINRD bit in the FLTEN register is set. The pulse limiting function can be turned off or the pulse duty cycle can be set to 1.6%, 3.1%, or 6.3% using the DU[1:0] bits in the INRP register. The MAX14002 does not provide a repetitive inrush pulse limiting feature.

#### **Diagnostic and Fault Reporting Features**

The MAX14001/MAX14002 continuously monitor seven possible fault conditions, and a hardware alert is provided via the open drain FAULT pin, which asserts low when an enabled fault is detected. The possible faults are: ADC

functionality error, repetitive inrush pulses being triggered, SPI framing error, loss of internal isolated data stream, CRC errors from internal communication, high-voltage FET failure, and corrupted memory error.

The bits in the FLTEN register determine how the FAULT output responds to the seven error conditions, and the FAULT output is asserted if the corresponding bit is enabled in the FLTEN register. If the FLTEN register bit DYEN = 0, FAULT operates as a latched output and remains asserted until the FLAGS register is cleared but if the bit DYEN = 1, FAULT operates as a dynamic output and de-asserts when the faults are no longer detected even though bits in the FLAGS register remain set.

If the corresponding bit in the FLTEN register is not set, when an error is flagged, FAULT will not be asserted, but the bit in the FLAGS register will still be latched and remain set until the register is read, which automatically clears all bits in the FLAGS register. Note that if a fault condition still exists when the register is read, the cleared fault bit will immediately be set again.

In a typical application, FAULT triggers an interrupt routine in the microcontroller or FPGA, which will read the FLAGS register to determine the cause of the interrupt.

#### **Diagnostic Conditions**

The diagnostic features implemented on the MAX14001/MAX14002 can be summarized as follows:

- 1) ADC Functionality Error: ADC functionality is checked by looking for changes in the ADC output. To ensure that a change should have occurred, a special test measurement is made while injecting a small current at the input of the ADC. This special measurement used for ADC functionality verification is interleaved between normal measurements and does not affect the ADC sampling time. If the ADC reading does not change, an ADC functional failure is declared and bit ADC (bit 1) in the FLAGS register is set.

- 2) Repetitive Inrush Pulses: If the repetitive inrush pulse limiting feature of the MAX14001 is turned on, and pulse limiting is triggered, bit INRD (bit 2) in the FLAGS register is set. See Repetitive Inrush Pulse Limiting (MAX14001 Only) for details on inrush pulse limiting.

- 3) SPI Framing Error: After  $\overline{CS}$  transitions from low to high, if the number of bits clocked in while  $\overline{CS}$  was low is not an integer multiple of 16, an SPI framing error is declared and bit SPI (bit 3) in the FLAGS register is set. The instruction in the SPI shift register is not decoded and no register value is changed.

- 4) Loss of Data Stream: The field-side sends ADC

## Configurable, Isolated 10-bit ADCs for Multi-Range Binary Inputs

data across the isolation barrier to the logic-side every 100µs, except for the startup period. If the periodic field-side data is not received, a loss of data stream fault is declared and bit COM (bit 4) in the FLAGS register is set. It is possible to recover from a loss of data stream fault by asserting a hard reset through the ACT register, which will return all of the registers to their default state, thus requiring the MAX14001/MAX14002 to go through the startup configuration process.

- 5) CRC Errors From Internal Communication: Internal communication across the isolation barrier includes a CRC code to ensure that corrupt data does not cause system problems. If the CRC indicates an error, the received data is discarded. If six consecutive CRCs fail, a CRC fault is declared and bit CRCL (bit 5) or CRCF (bit 6) in the FLAGS register is set.

- 6) **High-Voltage FET Failure:** If the ADC reading is greater than the inrush re-arm threshold (INRR), and IFET is not able to sink the programmed current, a FET fault is declared and bit FET (bit 7) in the FLAGS register is set. INRR is permanently set to 0x0C0 in MAX14002.

- 7) **Memory Error:** The devices continually compare the bits of each verification register to the bits of their corresponding configuration register. If any of the bits do not match, a memory fault is declared and bit MV (bit 8) in the FLAGS register is set. No information on which register failed is provided. Note that the default value for each verification register is the complement of its corresponding configuration register, which guarantees an MV fault any time power is lost and restored.

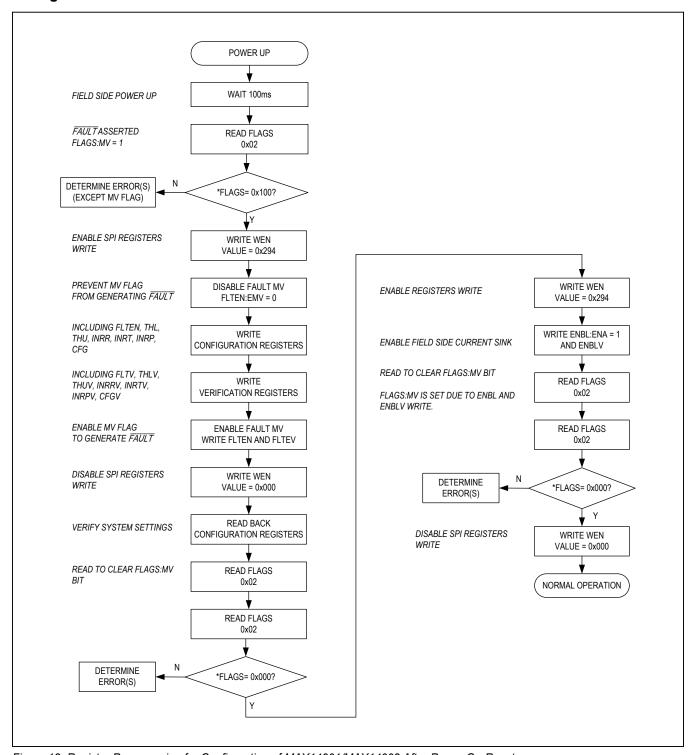

#### **FAULT** at Power-On

The devices' internal memory is volatile and must be reprogrammed after power cycling. To protect against undetected power glitches and the remote possibility that a memory bit would be lost during years of static operation, the devices monitor their configuration registers and assert bit MV (bit 8) in the FLAGS register any time the memory is corrupted. Verification registers have complementary POR values compared to the configuration registers, and therefore the MAX14001/MAX14002 start with a memory fault condition and assert the FAULT pin at startup.

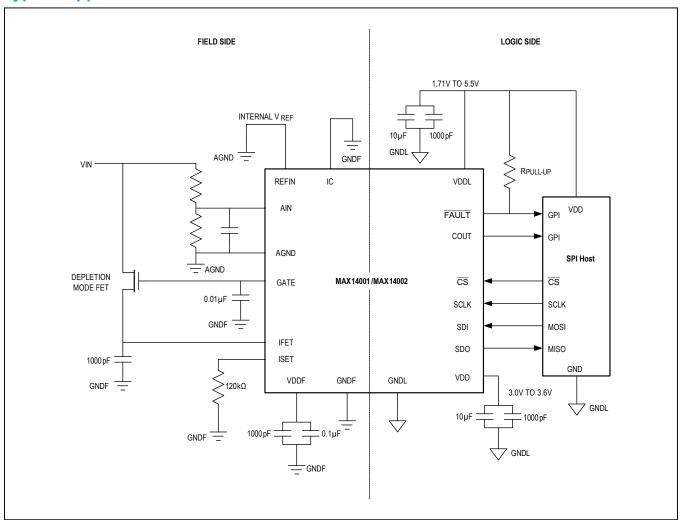

#### **Isolated Power and Data Transfer**

A simplified view of the isolated power and data transfer sections is shown in the <u>Functional Diagram</u>. The logic-side supply  $V_{DD}$  powers an integrated, inductively coupled, DC-DC converter that generates a nominal 3V with just enough output current to power the field-side of the MAX14001/MAX14002 and an external  $70\mu$ A voltage reference. No other circuits should be powered from the field-side of the MAX14001/MAX14002.

Serial data is transferred by capacitively-isolated differential transceivers. To verify reliable communication through the isolation barrier, a cyclic redundancy check (8-bit CRC) is embedded in the transmitted serial data streams. If a CRC fails, the data is discarded and no action is taken. If six consecutive CRCs fail, the CRC bit in the FLAGS register is set and FAULT is asserted if the CRC fault enable bit is set in the FLTEN register.

#### **Configuration and Monitoring**

An SPI interface is used for transferring configuration, control and diagnostic data as well as ADC readings between a master (FPGA or microcontroller) and single/multiple MAX14001/MAX14002(s). The interface can support daisy-chain configuration and consists of four ports: SCLK,  $\overline{CS}$ , SDI and SDO.

#### **SPI Interface**

SPI communication includes the following features:

- Support for daisy-chain operation

- Able to verify the previous command was correctly received by reading SDO on the next instruction cycle

- Able to read/verify all written registers (except ACT register)

- Identify when commands are not a multiple of 16-bits and set the SPI fault flag

- Commands of all 0s or all 1s do not change any writable registers

- A single command cannot program both the configuration and verification register

- Serial clock up to 5MHz

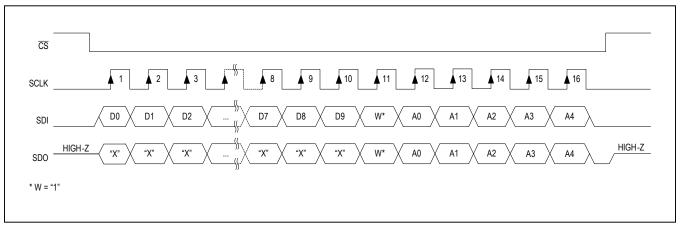

The command is 16-bits in length and the structure of the 16-bit data is shown in the Table 2.

#### **Table 2. SPI Command**

| ADDRESS                   | CONTROL                                   | DATA                       |

|---------------------------|-------------------------------------------|----------------------------|

| 5-bits A[4:0], MSB to LSB | $W/\overline{R}$ bit, Read = 0, Write = 1 | 10-bits D[9:0], MSB to LSB |

## Configurable, Isolated 10-bit ADCs for Multi-Range Binary Inputs

The first bit clocked into the SDI port is D[0], the data LSB (note: many SPI products clock MSB first so the microcontroller or FPGA needs to reverse data prior to outputting it to the MAX14001/MAX14002 SDI pin). As long as  $\overline{CS}$  is in a logic-low state, the SPI interface is working as a simple shift register, and SDI data is shifted on the rising edge of SCLK without decoding the commands. When  $\overline{\text{CS}}$  goes back to logic-high state, the bits in the shift register are decoded. If the command is a write, the data portion of the SPI shift register is copied to the specified register and the shift register is unchanged. If the command is a read, the content of the specified register is copied to the data portion of the SPI shift register, while the address bits A[4:0] and control bit  $W/\overline{R}$  are unchanged. The read action is completed during the next instruction cycle when  $\overline{\text{CS}}$  again goes to logic-low state and the contents of the shift register are clocked out of SDO on the falling edge of SCLK.

The functionality of each SPI pin can be summarized as follows.

**Serial Clock (SCLK):** Input for the master serial clock signal. The clock signal determines the speed of the data transfer (5MHz maximum) and all data transfers are synchronous to this clock. SCLK must remain low when  $\overline{\text{CS}}$  transitions are from high to low and from low to high. The number of SCLK rising edges that are received

during  $\overline{CS}$  logic-low state must be a multiple of 16. Otherwise, the received command will be ignored.

Chip Select  $(\overline{CS})$ : The  $\overline{CS}$  input enables the SPI interface. During a logic-low state, data is transferred on the edges of SCLK. A logic-high state on  $\overline{CS}$  forces SDO to high impedance mode and any SCLK transitions are ignored.

During a write cycle, the content of the shift register is transferred to the addressed internal register on the *rising edge* of  $\overline{CS}$ . During a read cycle, the content of the internal register that was addressed is transferred to the shift register on the *rising edge* of  $\overline{CS}$  and the data will be clocked out of the SDO pin during the next SPI cycle.

**Serial Input (SDI):** SDI or MOSI is the serial input port of the SPI shift register and data is clocked LSB first into the shift register on the *rising edge* of SCLK. On the rising edge of  $\overline{\text{CS}}$ , the input data is latched into the internal registers.

**Serial Output (SDO):** SDO or MISO is the serial output port of the SPI shift register, and is in a high impedance state until the  $\overline{\text{CS}}$  pin goes to logic-low state. Data is clocked LSB first out of the shift register on the *falling edge* of SCLK.

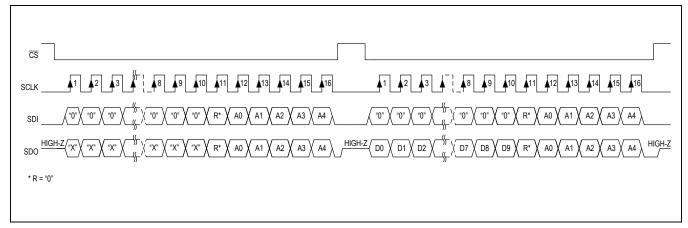

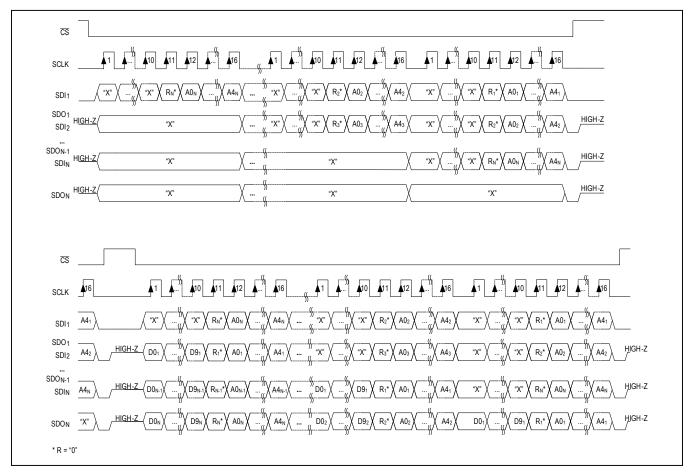

The SPI interface Read and Write Timing Diagrams are shown in Figure 6, Figure 7, and Figure 8.

Figure 6. SPI Write

Figure 7. SPI Read

Figure 8. SPI Timing Diagram

## Configurable, Isolated 10-bit ADCs for Multi-Range Binary Inputs

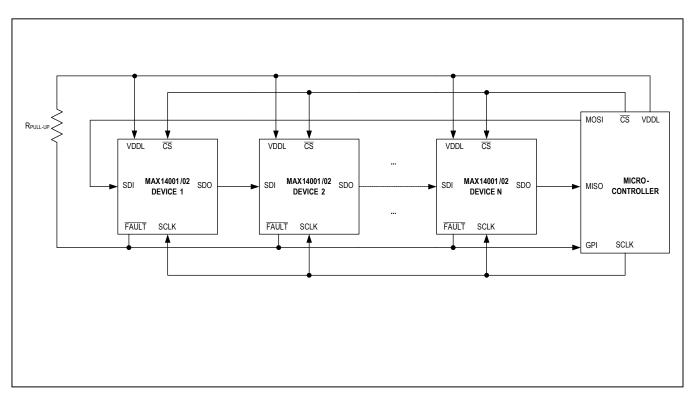

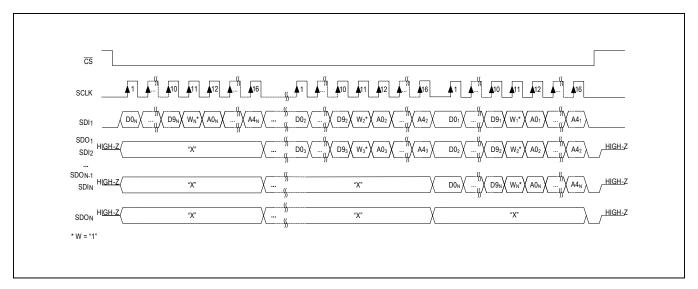

#### **Daisy-Chain SPI Operation**

The device supports daisy-chain operation, allowing control/monitoring of multiple MAX14001/MAX14002 devices from a single serial interface host with common

CS and SCLK signals as illustrated in Figure 9. The data that is clocked into SDI is clocked out of SDO with a 16-SCLK-cycle delay for each device in the daisy-chain, which is illustrated in Figure 10 and Figure 11.

Figure 9. Daisy-Chain Connection

Figure 10. SPI Daisy-Chain Write

Figure 11. SPI Daisy-Chain Read

The MAX14001/MAX14002 registers and their default Power-On-Reset (POR) values are shown in Table 3: Register Map

Table 3. Register Map

| 0         |       | 7    |                                            | ,     |      | ,                         | ,     |          | ļ                    |           |         | ,    | •       | 1       |

|-----------|-------|------|--------------------------------------------|-------|------|---------------------------|-------|----------|----------------------|-----------|---------|------|---------|---------|

| ADDR      | NAME  | IYPE | PURPUSE                                    | 6     | æ    | ,                         | ٥     | ဌ        | 4                    | 3         | 7       | -    | 0       | DEFAULI |

| 00×0      | ADC   | ď    | Unfiltered ADC reading                     |       |      |                           |       | ∢        | ADC[9:0]             |           |         |      |         |         |

| 0x01      | FADC  | ~    | Filtered ADC reading                       |       |      |                           |       | F/       | FADC[9:0]            |           |         |      |         |         |

| 0x02      | FLAGS | COR  | COR Error Flags                            | (9)X  | AM   | FET                       | CRCF  | CRCL     | COM                  | SPI       | INRD    | ADC  | ×       | 000×0   |

| 0×03      | FLTEN | RW   | FAULT Enable                               | ×     | EMV  | EFET                      | ECRCF | ECRCL    | ECOM                 | ESPI      | EINRD   | EADC | DYEN    | 0x1FF   |

| 0x04      | THL   | RW   | Lower Comparator<br>Threshold              |       |      |                           |       | 1        | THL[9:0]             |           |         |      |         | 0x100   |

| 0x05      | THU   | RW   | Upper Comparator<br>Threshold              |       |      |                           |       | <b>–</b> | THU[9:0]             |           |         |      |         | 0x200   |

| 90×0      | INRR  | RW*  | Inrush Re-arm<br>Threshold <sup>(1)</sup>  |       |      |                           |       | <u>N</u> | INRR[9:0]            |           |         |      |         | 0x0C0   |

| 0×07      | INRT  | KW*  | Inrush Trigger<br>Threshold <sup>(2)</sup> |       |      |                           |       | 4        | INRT[9:0]            |           |         |      |         | 0x180   |

| 0×08      | INRP  | KW*  | Inrush Pulse <sup>(3)</sup>                |       | Z    | IINR[3:0] <sup>(4)</sup>  |       |          | TINF                 | TINR[3:0] |         | lna  | DU[1:0] | 0x1D8   |

| 60×0      | CFG   | RW   | Configuration                              |       | IBIA | IBIAS[3:0] <sup>(5)</sup> |       | EXRF     | EXTI                 | FT[       | FT[1:0] | FAST | IRAW    | 0x183   |

| 0x0A      | ENBL  | RW   | Enable                                     | ×     | ×    | ×                         | ×     | ×        | ENA                  | ×         | ×       | ×    | ×       | 0x000   |

| 0x0B      | ACT   | WC   | Action                                     | INPLS | ×    | RSET                      | SRES  | ×        | ×                    | ×         | ×       | ×    | ×       | 0x000   |

| 0x0C      | WEN   | RW   | Write Enable                               |       |      |                           |       | <b>M</b> | WEN[9:0]             |           |         |      |         | 0x000   |

| 0x0D-0x12 |       |      | Reserved                                   |       |      |                           |       | Reserve  | Reserved. Do not use | )e        |         |      |         |         |

| 0x13      | FLTV  | RW   | FLTEN Verification                         |       |      |                           |       | H        | FLTV[9:0]            |           |         |      |         | 0x000   |

| 0x14      | THLV  | RW   | THL Verification                           |       |      |                           |       | Ţ        | THLV[9:0]            |           |         |      |         | 0x2FF   |

| 0x15      | THUV  | RW   | THU Verification                           |       |      |                           |       | <u> </u> | THUV[9:0]            |           |         |      |         | 0x1FF   |

| 0x16      | INRRV | RW.  | RW* INRR Verification <sup>(1)</sup>       |       |      |                           |       | Ž        | INRRV[9:0]           |           |         |      |         | 0x33F   |

| 0x17      | INRTV | RW.  | RW* INRT Verification(2)                   |       |      |                           |       | Z        | INRTV[9:0]           |           |         |      |         | 0x27F   |

| 0x18      | INRPV | RW*  | INRP Verification(3)                       |       |      |                           |       | N        | INRPV[9:0]           |           |         |      |         | 0x227   |

| 0x19      | CFGV  | RW   | CFG Verification                           |       |      |                           |       | S        | CFGV[9:0]            |           |         |      |         | 0x27C   |

| 0x1A      | ENBLV | RW   | Enable Verification                        |       |      |                           |       | EN       | ENBLV[9:0]           |           |         |      |         | 0x3FF   |

| 0x1B-0x1F |       |      | Reserved                                   |       |      |                           |       | Reserve  | Reserved. Do not use | şe.       |         |      |         |         |

|           |       |      |                                            |       |      |                           |       |          |                      |           |         |      |         |         |

<sup>\*</sup> Register is read only for the MAX14002

6. "x" is unused.

<sup>1:</sup> INRR = INRRV = 0x0C0 for MAX14002

<sup>3:</sup> INRP = INRPV = 0x1D8 for MAX14002 2: INRT = INRTV = 0x180 for MAX14002

<sup>4:</sup> Setting IINR = 0 forces IFET = 50µA

<sup>5:</sup> Setting IBIAS = 0 forces IFET = 50µA

### **Register Type Legend:**

R - Read only

RW - Read and write

COR - Latched read only, clear on read

WC - Write and clear (Write only, executes and clears immediately)

#### **Register Detailed Description**

### ADC (Read)

#### Address = 0x00

| BIT | FIELD NAME | DESCRIPTION                                       |

|-----|------------|---------------------------------------------------|

| 9:0 | ADC[9:0]   | Contains the latest ADC reading (straight binary) |

#### FADC (Read)

#### Address = 0x01

| BIT | FIELD NAME | DESCRIPTION                                                                                           |

|-----|------------|-------------------------------------------------------------------------------------------------------|

| 9:0 | FADC[9:0]  | Contains the latest filtered ADC reading as set by bits FT[1:0] in the CFG register (straight binary) |

### FLAGS (Latched, Clear On Read)

#### Address = 0x02

#### Default = 0x000

Latched flags indicate errors and why the FAULT pin was asserted if the fault is enabled in the FLTEN register. Reading the register clears all flags.

Note: Faults conditions are latched and the relevant bits are set; reading the value of this register will reset the fault flags that are not active anymore. However, if the fault is still valid, reading the FLAGS register will not be able to clear the specific bit.

| BIT | FIELD NAME | DESCRIPTION                                                                      |

|-----|------------|----------------------------------------------------------------------------------|

| 0   | FLAG0      | Unused                                                                           |

| 1   | ADC        | ADC reading stuck at one value                                                   |

| 2   | INRD       | Exceeding specified duty-cycle for the inrush current                            |

| 3   | SPI        | Number of bits clocked in while CS was asserted is not an integer multiple of 16 |

| 4   | СОМ        | Field-side communication failure                                                 |

| 5   | CRCL       | Field-to-logic-side transmission had 6 consecutive CRC errors reported           |

| 6   | CRCF       | Logic-to-field-side transmission had 6 consecutive CRC errors reported           |

| 7   | FET        | Input voltage detected without input current                                     |

| 8   | MV         | Failed memory validation                                                         |

| 9   | FLAG9      | Unused                                                                           |

#### **FLTEN (Read/Write)**

Address = 0x03

Default = 0x1FF

Enables fault conditions to assert the FAULT signal.

Note: Fault enable bits only effect fault reporting through the  $\overline{FAULT}$  pin. Bits in the FLAGS register will be set regardless whether fault is enabled or disabled by the FLTEN register.

| BIT | FIELD NAME | DESCRIPTION                                                                                                                                                   |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | DYEN       | 0: FAULT is latched; it is cleared after the FLAGS register is read.  1: FAULT is dynamic; it is cleared as soon as the fault condition disappears. (Default) |

| 1   | EADC       | 0: Prevents ADC error from asserting FAULT  1: Allows ADC error to assert FAULT (Default)                                                                     |

| 2   | EINRD      | 0: Prevents INRD error from asserting FAULT  1: Allows INRD error to assert FAULT (Default)                                                                   |

| 3   | ESPI       | 0: Prevents SPI error from asserting FAULT 1: Allows SPI error to assert FAULT (Default)                                                                      |

| 4   | ECOM       | 0: Prevents COM error from asserting FAULT  1: Allows COM error to assert FAULT (Default)                                                                     |

| 5   | ECRCL      | 0: Prevents CRCL error from asserting FAULT 1: Allows CRCL error to assert FAULT (Default)                                                                    |

| 6   | ECRCF      | 0: Prevents CRCF error from asserting FAULT 1: Allows CRCF error to assert FAULT (Default)                                                                    |

| 7   | EFET       | 0: Prevents FET error from asserting FAULT  1: Allows FET error to assert FAULT (Default)                                                                     |

| 8   | EMV        | 0: Prevents MV error from asserting FAULT 1: Allows MV error to assert FAULT (Default)                                                                        |

| 9   | FLTEN9     | Unused                                                                                                                                                        |

#### THL (Read/Write)

Address = 0x04

Default = 0x100

User-programmed lower comparator threshold. When the output of the comparator is high, this value is compared to ADC (or FADC as set by IRAW, FT0 and FT1). If ADC ≤ THL, the comparator output COUT is set low. To prevent oscillation, the value of THL should be smaller than THU.

| BIT | FIELD NAME | DESCRIPTION                                  |

|-----|------------|----------------------------------------------|

| 9:0 | THL[9:0]   | Lower comparator threshold (straight binary) |

#### **THU (Read/Write)**

Address = 0x05

Default = 0x200

User-programmed upper comparator threshold. When the output of the comparator is low, this value is compared to ADC (or FADC as set by IRAW, FT0, and FT1). If ADC ≥ THU, the comparator output COUT is set high. To prevent oscillation, the value of THU should be larger than THL.

| E | BIT | FIELD NAME | DESCRIPTION                                  |

|---|-----|------------|----------------------------------------------|

|   | 9:0 | THU[9:0]   | Upper comparator threshold (straight binary) |

### INRR (Read/Write) (Read only for MAX14002)

Address = 0x06

Default = 0x0C0

User-programmed inrush timer re-arm threshold. ADC reading must drop below this value before another inrush pulse will occur when the input voltage exceeds INRT. This register is not used in the MAX14002, which always uses FAST mode (see bit 1 of the CFG register).

| BIT | FIELD NAME | DESCRIPTION                               |

|-----|------------|-------------------------------------------|

| 9:0 | INRR[9:0]  | Inrush re-arm threshold (straight binary) |

### INRT (Read/Write) (Ready only for MAX14002)

Address = 0x07

Default = 0x180

User-programmed inrush current trigger threshold. When the inrush timer is armed, an inrush pulse is initiated when the ADC reading equals or exceeds this value. This register is not used in the MAX14002, which always uses FAST mode (see bit 1 of the CFG register).

| BIT | FIELD NAME | DESCRIPTION                                |

|-----|------------|--------------------------------------------|

| 9:0 | INRT[9:0]  | Inrush trigger threshold (straight binary) |

## INRP (Read/Write) (Read only for MAX14002)

Address = 0x08

Default = 0x1D8

Contains user-programmed values for the inrush current pulse magnitude, inrush pulse duration, and inrush pulse duty cycle.

| IT  | FIELD NAME | DESCRIPTION                                                                                                                                                                                                                                  |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:0 | DU[1:0]    | DU1 and DU0 set the maximum duty cycle for inrush current over the last 10 seconds.  DU[1:0] = 00 Duty Cycle limiting function off (Default)  DU[1:0] = 01 Duty Cycle = 1.6%  DU[1:0] = 10 Duty Cycle = 3.1%  DU[1:0] = 11 Duty Cycle = 6.3% |

| 5:2 | TINR[3:0]  | 4-bit inrush time, 0 to 120ms in 8ms steps, straight binary TINR[3:0] = 0000 = 0ms TINR[3:0] = 0001 = 8ms TINR[3:0] = 0110 = 48ms (Default) TINR[3:0] = 1110 = 112ms TINR[3:0] = 1111 = 120ms                                                |

| 9:6 | IINR[3:0]  | 4-bit inrush current, 50μA to 105mA in 7mA steps, straight binary IINR[3:0] = 0000 = 50μA IINR[3:0] = 0001 = 7mA  IINR[3:0] = 0111 = 49mA (Default)  IINR[3:0] = 1110 = 98mA IINR[3:0] = 1111 = 105mA                                        |

## **CFG** (Read/Write)

Address = 0x09

Default = 0x183

Configuration register controls functions within the MAX14001/MAX14002.

| BIT | FIELD NAME | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                           |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | IRAW       | Selects Inrush comparator input multiplexer.  0: Inrush comparator input is connected to filtered data in the FADC register  1: Inrush comparator input is connected to 'raw' data in the ADC register (default)                                                                                                                                                                      |