## MCF51QM128 Reference Manual

Supports the MCF51QM32, MCF51QM64, and MCF51QM128

Document Number: MCF51QM128RM

Rev. 4, 08/2012

#### **Contents**

| Section number |         |              | Title                              | Page |

|----------------|---------|--------------|------------------------------------|------|

|                |         |              | Chapter 1 About This Document      |      |

| 1.1            | Overvi  | ew           |                                    | 57   |

|                | 1.1.1   | Purpose      |                                    | 57   |

|                | 1.1.2   | Audience     | <u> </u>                           | 57   |

| 1.2            | Conve   | ntions       |                                    | 57   |

|                | 1.2.1   | Numberii     | ng systems                         | 57   |

|                | 1.2.2   | Typograp     | phic notation                      | 58   |

|                | 1.2.3   | Special te   | erms                               | 58   |

|                | 1.2.4   | Register     | reset                              | 59   |

|                |         |              | Chapter 2<br>Introduction          |      |

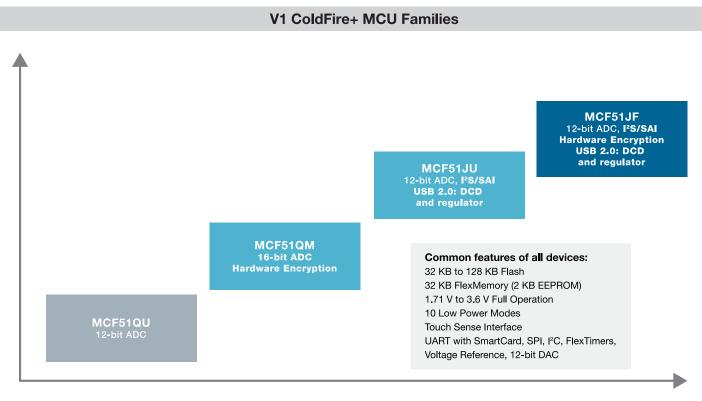

| 2.1            | ColdFi  | re+ Portfoli | o Introduction                     | 61   |

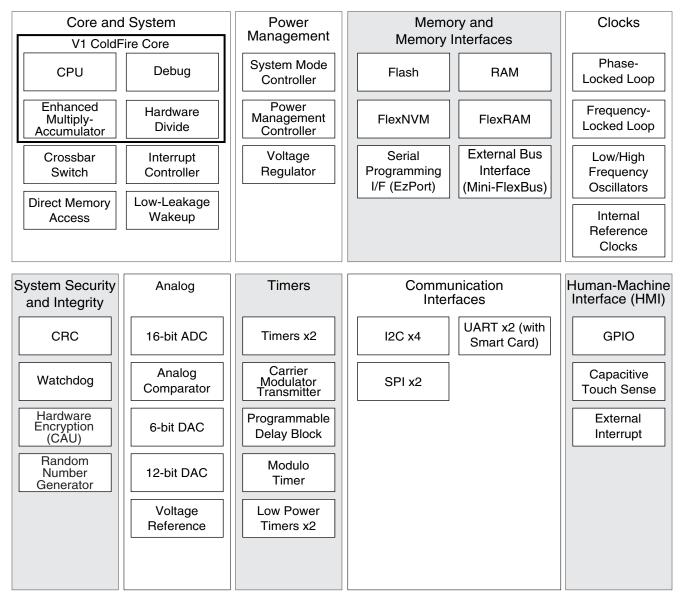

| 2.2            | MCF5    | 1QM128 B1    | ock Diagram                        | 62   |

| 2.3            | MCF5    | 1QM Featur   | e Summary                          | 63   |

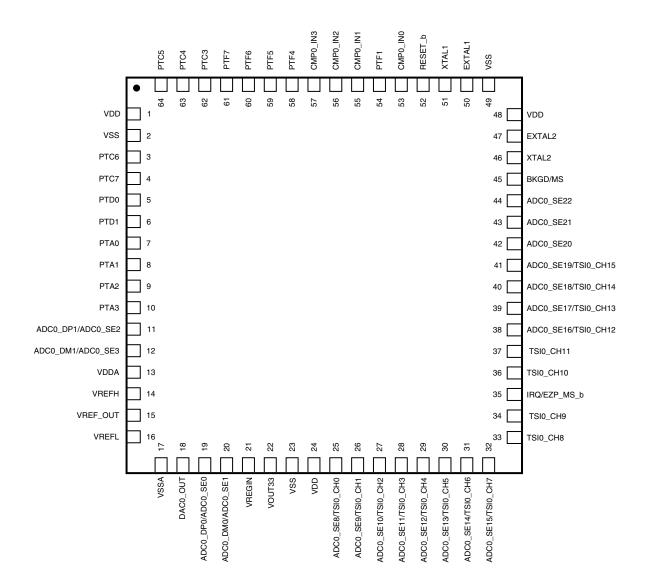

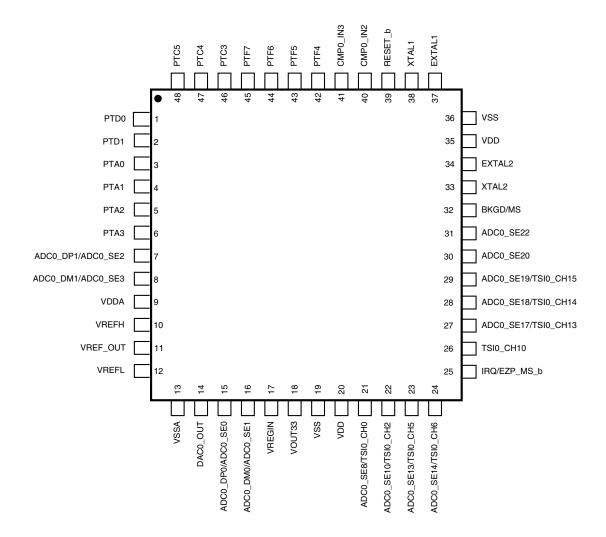

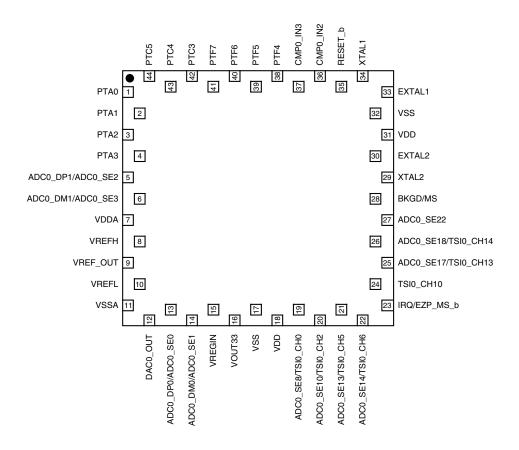

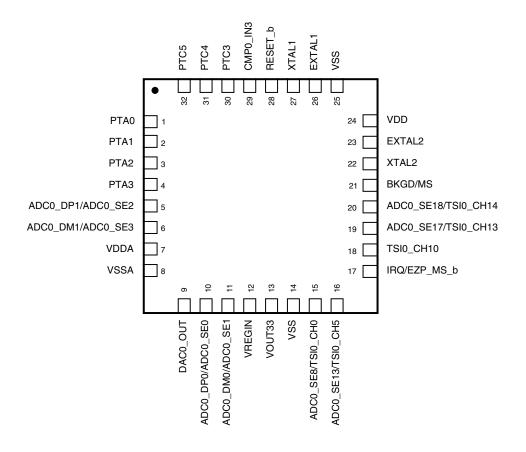

| 2.4            | MCF5    | 1QM Featur   | res by Package                     | 67   |

|                |         |              | Chapter 3 Chip Configuration       |      |

| 3.1            | Introdu | action       |                                    | 69   |

| 3.2            | Modul   | e to Module  | Interaction Summary                | 69   |

| 3.3            | Core n  | nodules      |                                    | 71   |

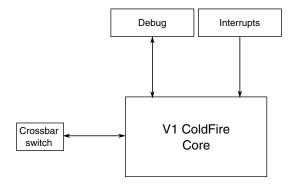

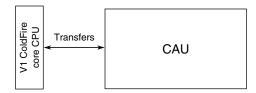

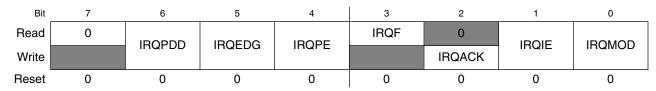

|                | 3.3.1   | Version 1    | (V1) ColdFire Core Configuration   | 71   |

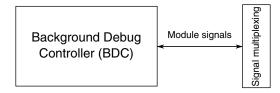

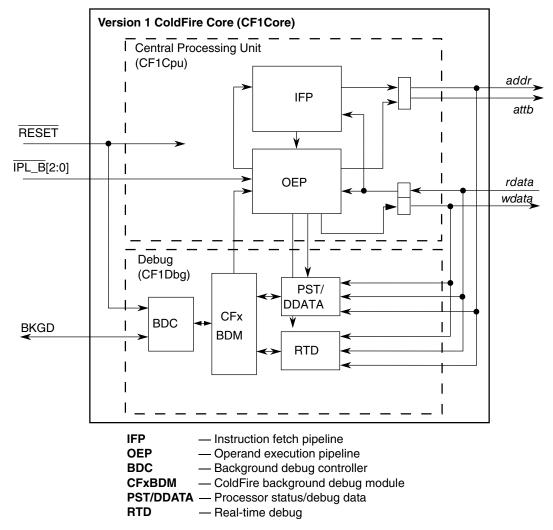

|                | 3.3.2   | Debug Co     | onfiguration                       | 71   |

|                |         | 3.3.2.1      | VREG in BDM                        | 72   |

| 3.4            | System  | n modules    |                                    | 72   |

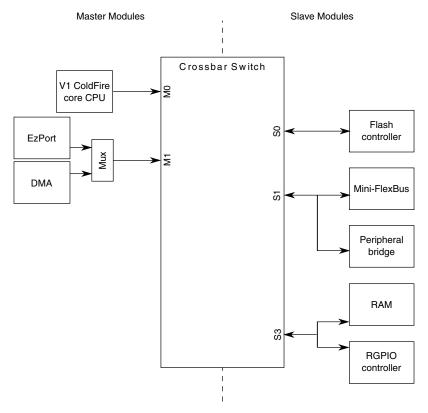

|                | 3.4.1   | Crossbar     | Switch Configuration               | 72   |

|                |         | 3.4.1.1      | Crossbar Switch Master Assignments | 73   |

|                |         | 3.4.1.2      | Crossbar Switch Slave Assignments  | 74   |

| Sec | tion nu | ımber     | Title                                                      | Page |

|-----|---------|-----------|------------------------------------------------------------|------|

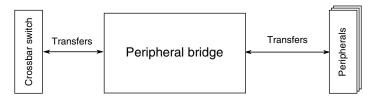

|     | 3.4.2   | Periphera | ll Bridge Configuration                                    | 74   |

|     |         | 3.4.2.1   | Peripheral bridge interfaces                               | 74   |

|     |         | 3.4.2.2   | Memory map and module register access                      | 75   |

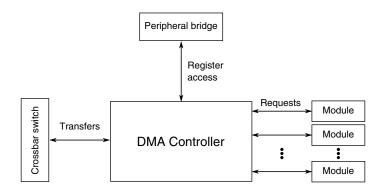

|     | 3.4.3   | DMA Co    | ntroller Configuration                                     | 75   |

|     |         | 3.4.3.1   | DMA Request Sources                                        | 75   |

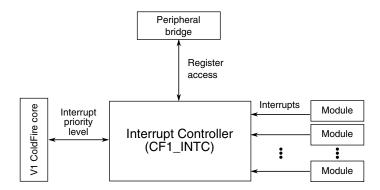

|     | 3.4.4   | Interrupt | Controller (INTC) Configuration.                           | 76   |

|     |         | 3.4.4.1   | Interrupt priority levels                                  | 77   |

|     |         | 3.4.4.2   | Interrupt channel assignments.                             | 77   |

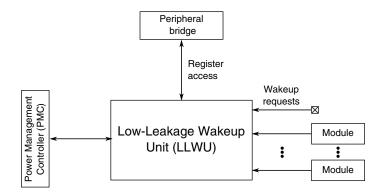

|     | 3.4.5   | Low-Leal  | kage Wakeup Unit (LLWU) Configuration                      | 79   |

|     |         | 3.4.5.1   | LLWU wakeup sources                                        | 80   |

|     |         | 3.4.5.2   | Reset due to LLWU wakeup event                             | 81   |

|     |         | 3.4.5.3   | LLWU register reset                                        | 81   |

|     | 3.4.6   | Computer  | r Operating Properly (COP) Watchdog Configuration          | 82   |

|     |         | 3.4.6.1   | COP clocks                                                 | 82   |

|     |         | 3.4.6.2   | COP watchdog operation.                                    | 82   |

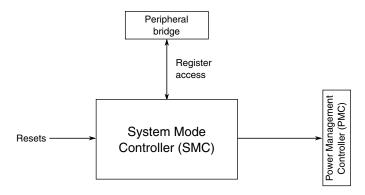

|     | 3.4.7   | System M  | Mode Controller (SMC) Configuration                        | 84   |

|     |         | 3.4.7.1   | SMC register reset.                                        | 84   |

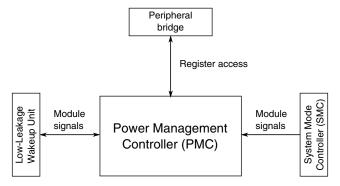

|     | 3.4.8   | Power Ma  | anagement Controller (PMC) Configuration                   | 85   |

|     |         | 3.4.8.1   | PMC register reset.                                        | 85   |

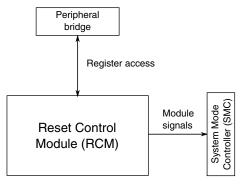

|     | 3.4.9   | Reset Cor | ntrol Module (RCM) Configuration.                          | 85   |

|     |         | 3.4.9.1   | RCM register reset.                                        | 86   |

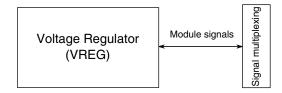

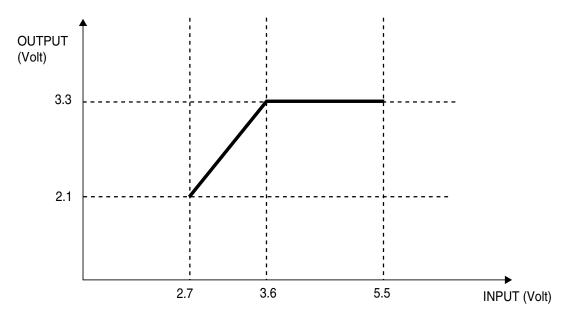

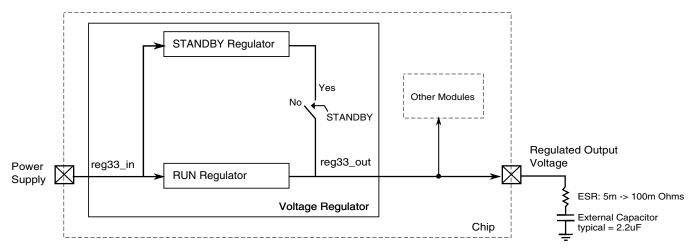

|     | 3.4.10  | Voltage F | Regulator (VREG) Configuration.                            | 86   |

|     |         | 3.4.10.1  | VREG operation controls.                                   | 87   |

|     |         | 3.4.10.2  | VREG in BDM                                                | 87   |

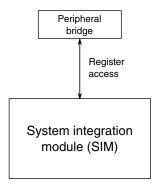

|     | 3.4.11  | System In | ntegration Module (SIM) Configuration                      | 87   |

|     |         | 3.4.11.1  | SIM register reset                                         | 88   |

| 3.5 | Clock N | Modules   |                                                            | 88   |

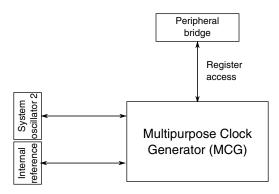

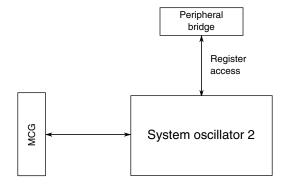

|     | 3.5.1   | Multipurp | pose Clock Generator (MCG) Configuration                   | 88   |

|     |         | 3.5.1.1   | MCG oscillator-frequency trim settings: factory and custom | 89   |

|     |         |           |                                                            |      |

| Section number |         |             | Title                                        | Page |

|----------------|---------|-------------|----------------------------------------------|------|

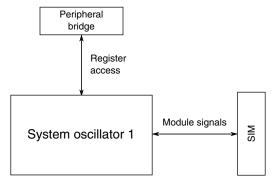

|                | 3.5.2   | Oscillator  | or (OSC) Configuration                       | 90   |

| 3.6            | Memor   | ries and Me | emory Interfaces.                            | 91   |

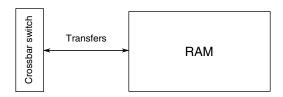

|                | 3.6.1   | RAM Co      | onfiguration                                 | 91   |

|                |         | 3.6.1.1     | RAM overview.                                | 91   |

|                |         | 3.6.1.2     | RAM sizes                                    | 91   |

|                |         | 3.6.1.3     | RAM retention in low power modes             | 92   |

|                |         | 3.6.1.4     | RAM accesses                                 | 92   |

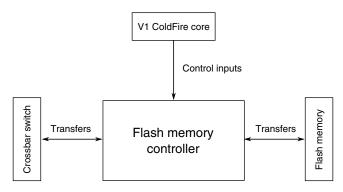

|                | 3.6.2   | Flash Me    | emory Controller (FMC) Configuration         | 92   |

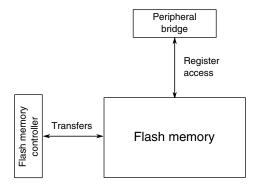

|                | 3.6.3   | Flash Me    | emory Module (FTFL) Configuration            | 93   |

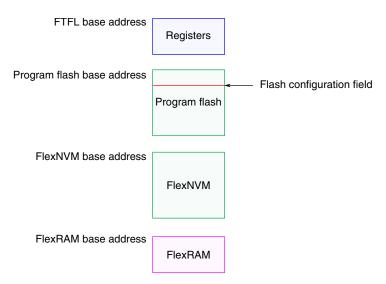

|                |         | 3.6.3.1     | Flash Memory Types                           | 94   |

|                |         | 3.6.3.2     | Flash Memory Sizes.                          | 94   |

|                |         | 3.6.3.3     | Flash Memory Map                             | 95   |

|                |         | 3.6.3.4     | Flash Security                               | 96   |

|                |         | 3.6.3.5     | Flash Modes                                  | 96   |

|                |         | 3.6.3.6     | Erase All Flash Contents                     | 96   |

|                |         | 3.6.3.7     | FTFL_FOPT Register                           | 96   |

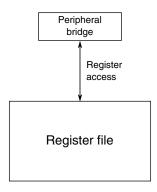

|                | 3.6.4   | System R    | Register File Configuration                  | 96   |

|                |         | 3.6.4.1     | Register file details                        | 97   |

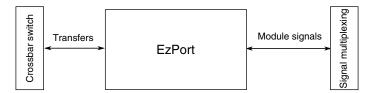

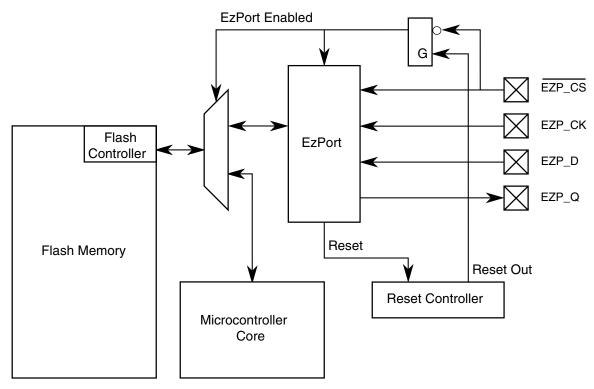

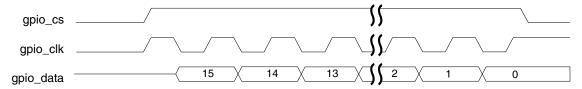

|                | 3.6.5   | EzPort C    | 'onfiguration                                | 97   |

|                |         | 3.6.5.1     | EzPort and BDM                               | 98   |

|                |         | 3.6.5.2     | Flash Option Register (FOPT)                 | 98   |

|                |         | 3.6.5.3     | EzPort Clocking                              | 98   |

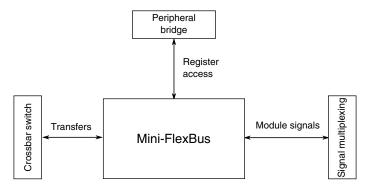

|                | 3.6.6   | Mini-Fle    | xBus Configuration                           | 99   |

|                |         | 3.6.6.1     | Mini-FlexBus instantiation information       | 99   |

|                |         | 3.6.6.2     | Mini-FlexBus CSCR0 reset value               | 100  |

|                |         | 3.6.6.3     | Mini-FlexBus security                        | 100  |

| 3.7            | Securit | y           |                                              | 100  |

|                | 3.7.1   | Cryptogra   | raphic Acceleration Unit (CAU) Configuration | 100  |

| Section number |        | ımber      | Title                                               | Page |

|----------------|--------|------------|-----------------------------------------------------|------|

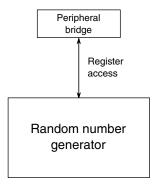

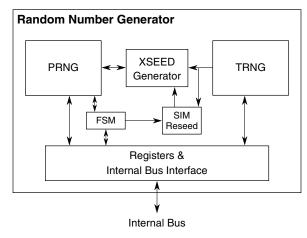

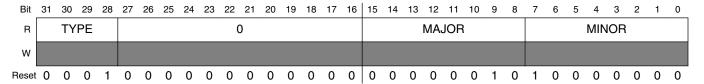

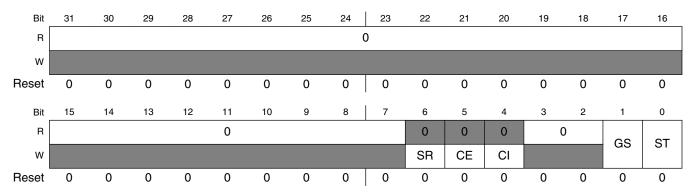

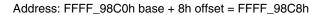

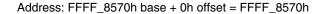

|                | 3.7.2  | Random 1   | Number Generator (RNG) Configuration                | 101  |

|                |        | 3.7.2.1    | Module register width and serialization of accesses | 101  |

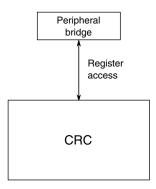

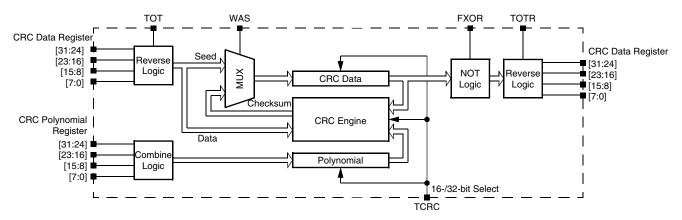

|                | 3.7.3  | Cyclic Re  | edundancy Check (CRC) Configuration                 | 102  |

|                |        | 3.7.3.1    | Module register width and serialization of accesses | 102  |

| 3.8            | Analog |            |                                                     | 102  |

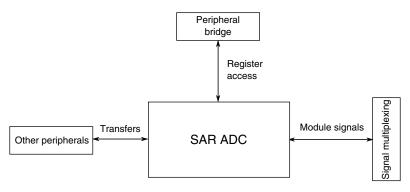

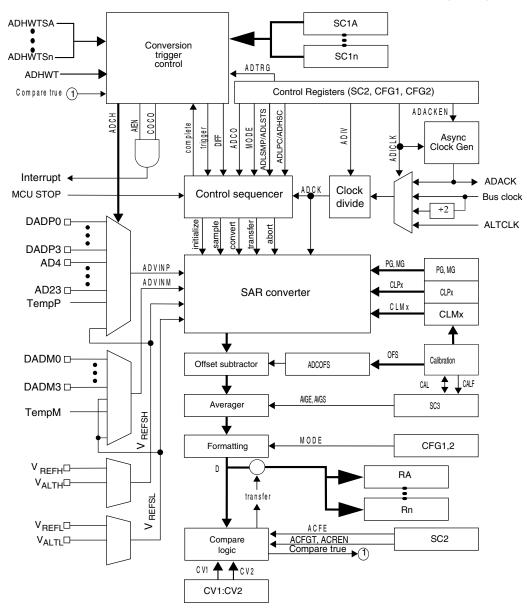

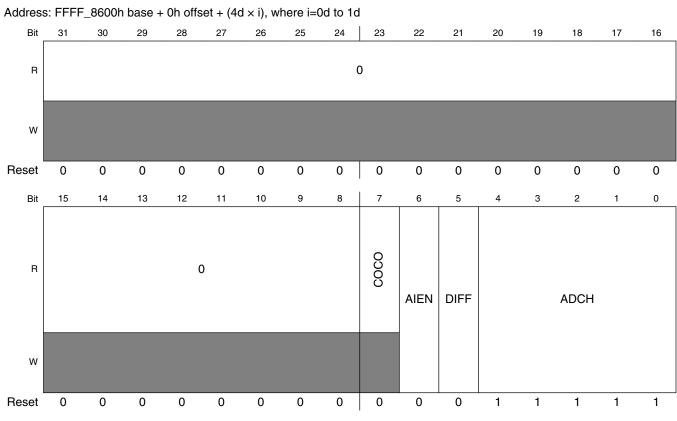

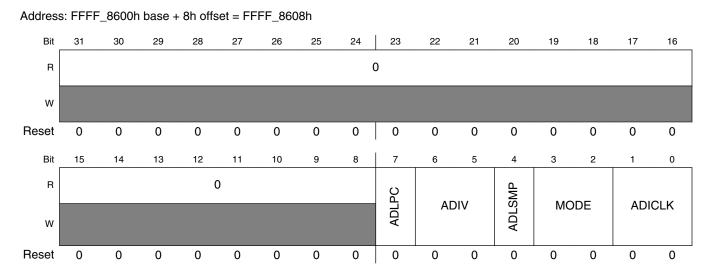

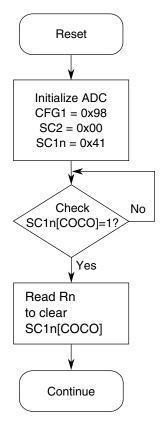

|                | 3.8.1  | 16-bit An  | nalog-to-Digital Converter (ADC) Configuration      | 102  |

|                |        | 3.8.1.1    | Module register width and serialization of accesses | 103  |

|                |        | 3.8.1.2    | ADC instantiation information                       | 103  |

|                |        | 3.8.1.3    | DMA support on ADC                                  | 103  |

|                |        | 3.8.1.4    | ADC0 Channel Assignments.                           | 104  |

|                |        | 3.8.1.5    | ADC Reference, Triggers, and Alternate Clock        | 105  |

|                |        | 3.8.1.6    | Clock Gating                                        | 105  |

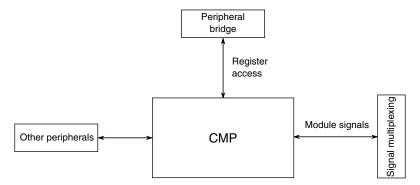

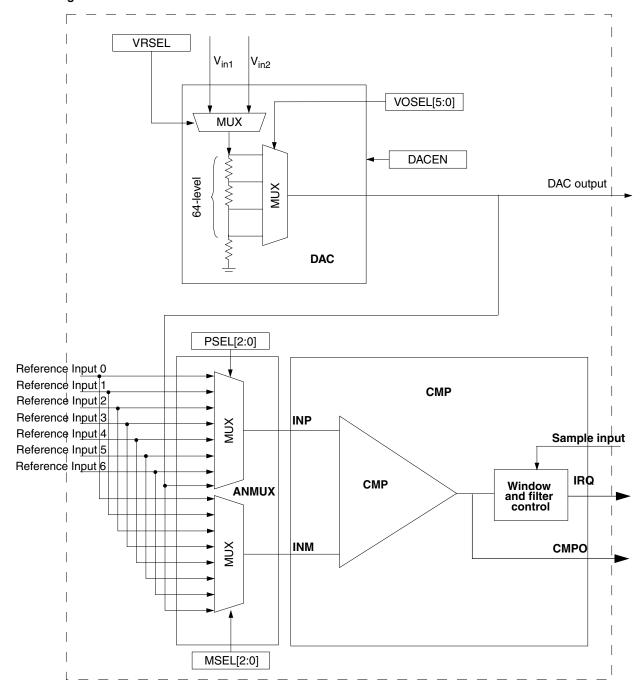

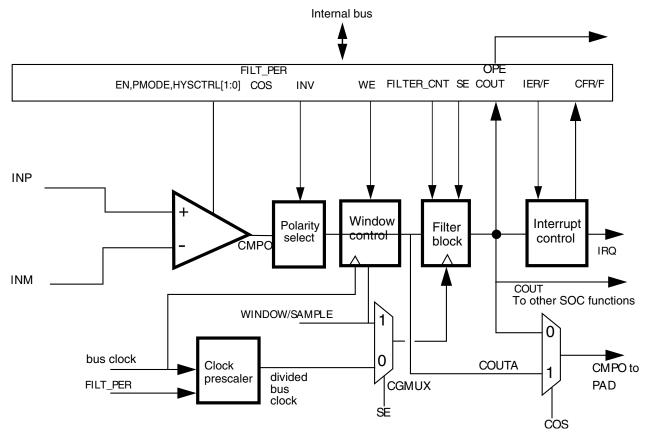

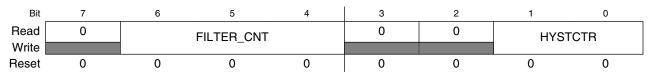

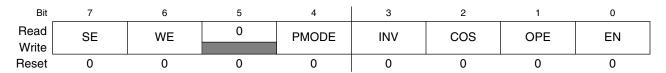

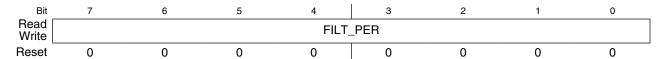

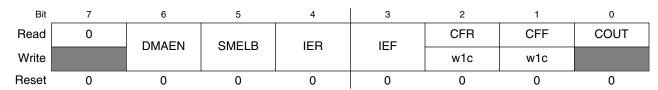

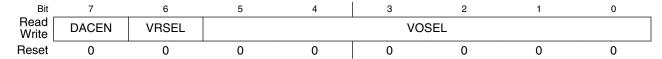

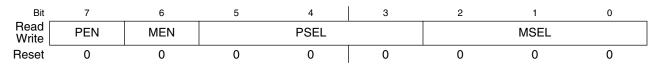

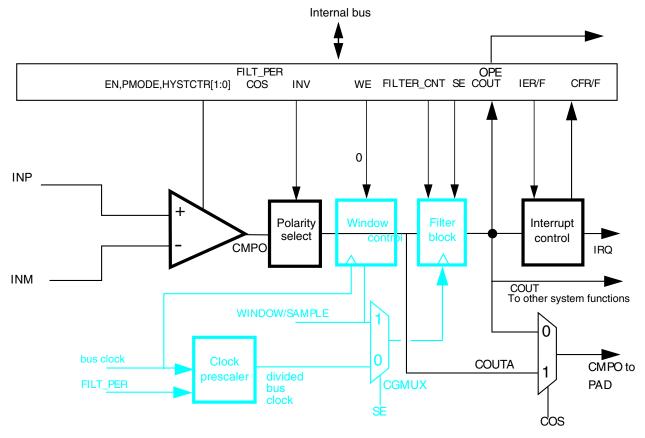

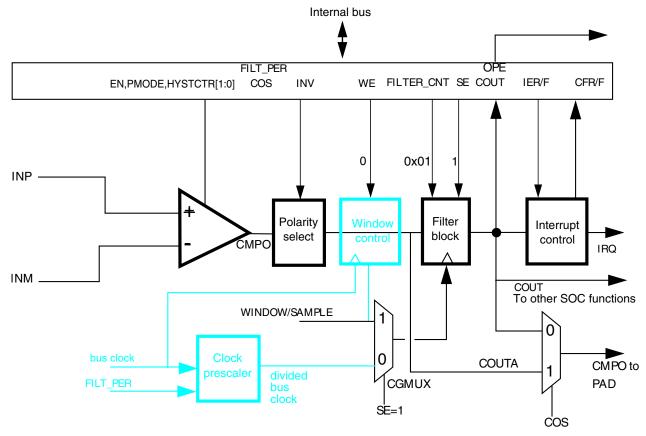

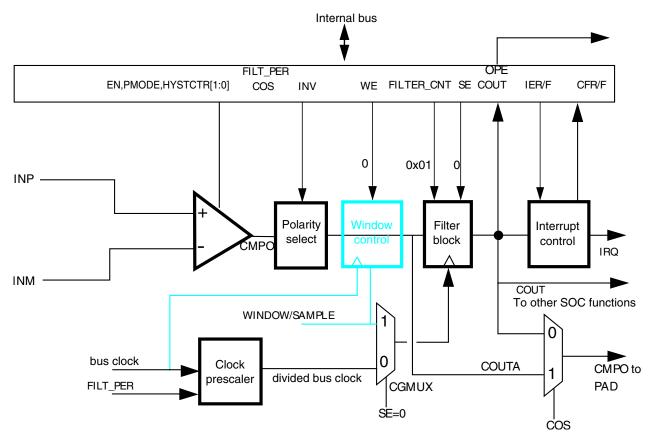

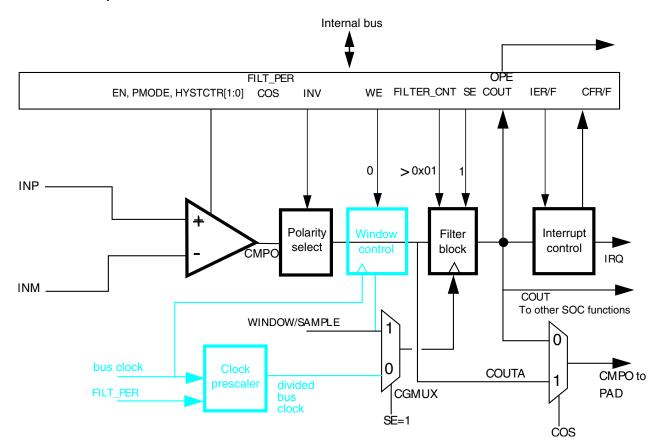

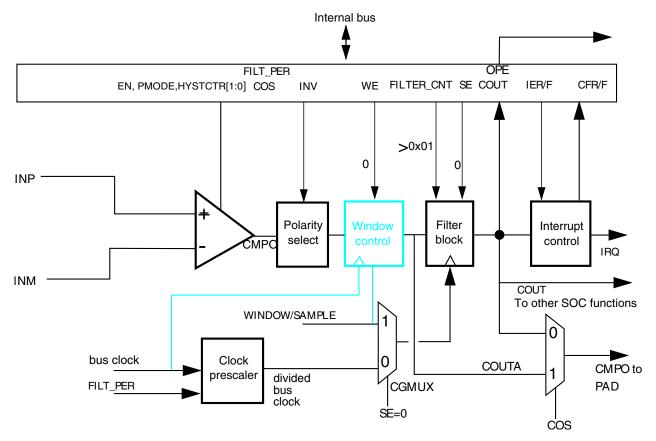

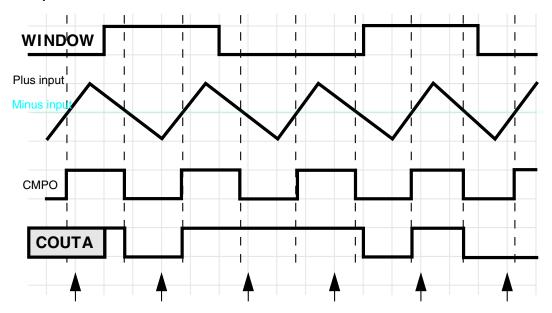

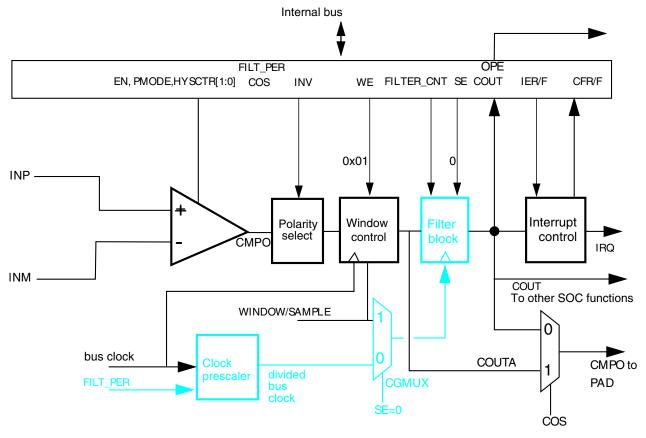

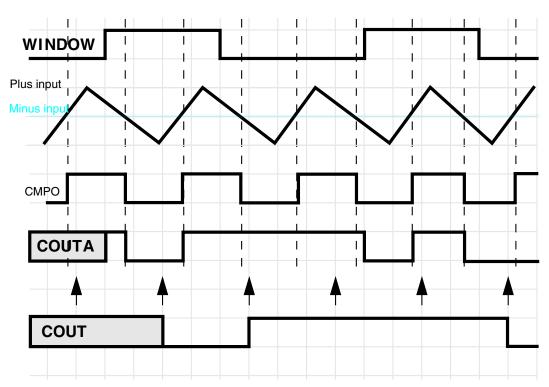

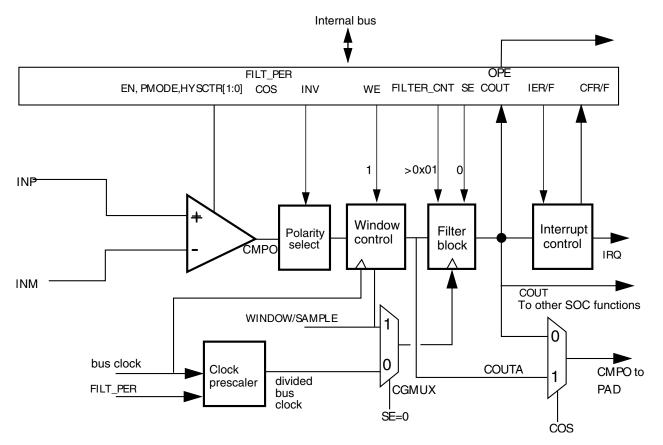

|                | 3.8.2  | Comparat   | tor (CMP) Configuration.                            | 106  |

|                |        | 3.8.2.1    | CMP instantiation information.                      | 106  |

|                |        | 3.8.2.2    | External window/sample input                        | 107  |

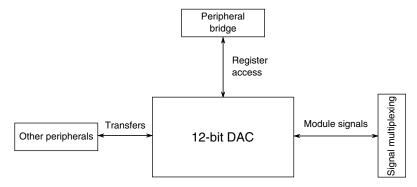

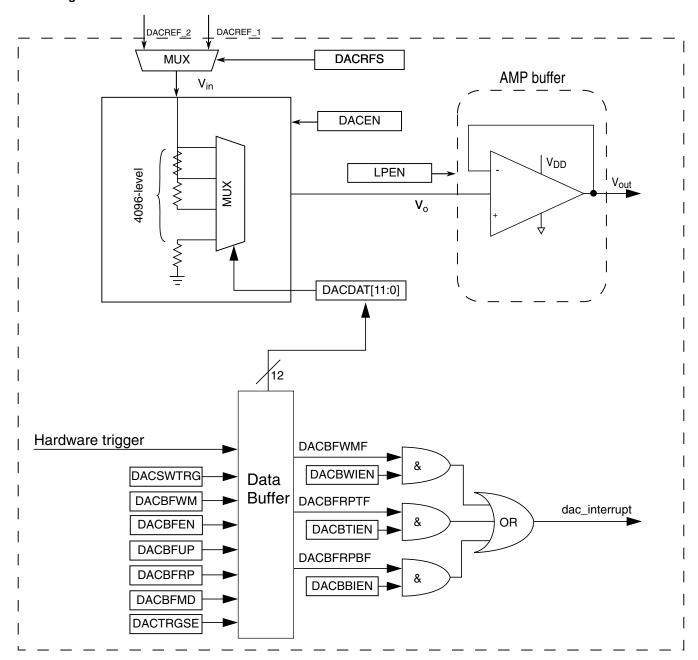

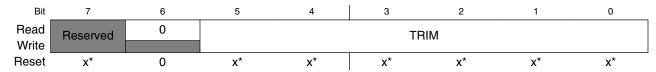

|                | 3.8.3  | 12-bit Dig | gital-to-Analog Converter (DAC) Configuration       | 108  |

|                |        | 3.8.3.1    | 12-bit DAC Overview                                 | 108  |

|                |        | 3.8.3.2    | 12-bit DAC Instantiation                            | 108  |

|                |        | 3.8.3.3    | 12-bit DAC Reference                                | 108  |

|                |        | 3.8.3.4    | DAC DMA request                                     | 109  |

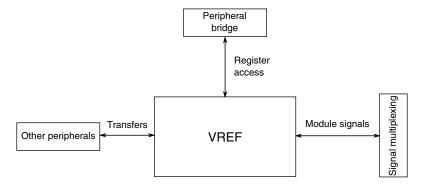

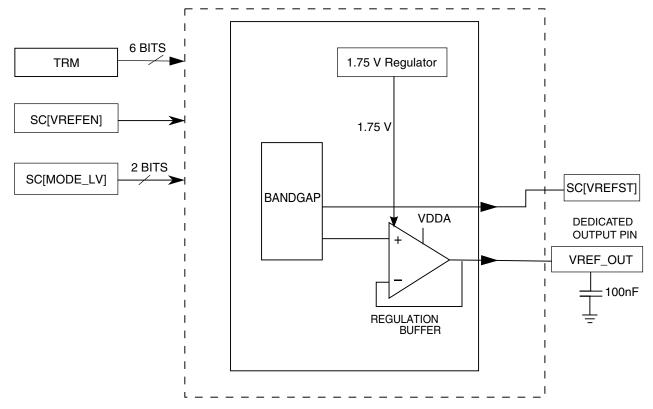

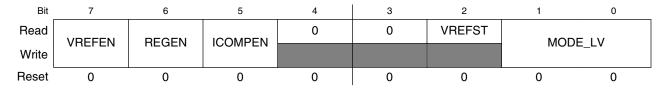

|                | 3.8.4  | Voltage F  | Reference (VREF) Configuration                      | 109  |

|                |        | 3.8.4.1    | VREF Overview                                       | 109  |

| 3.9            | Timers |            |                                                     | 110  |

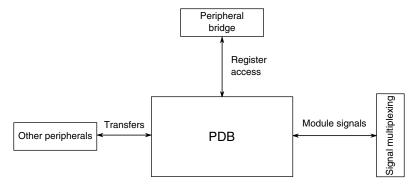

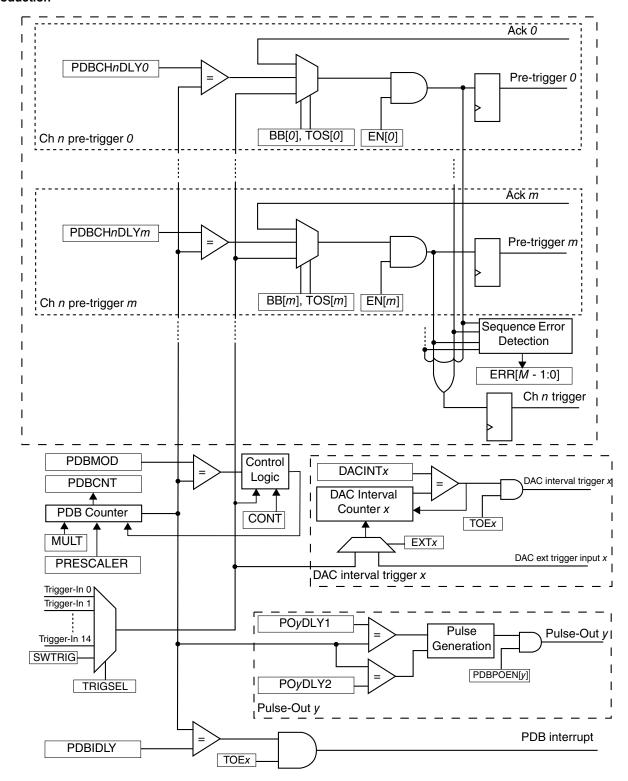

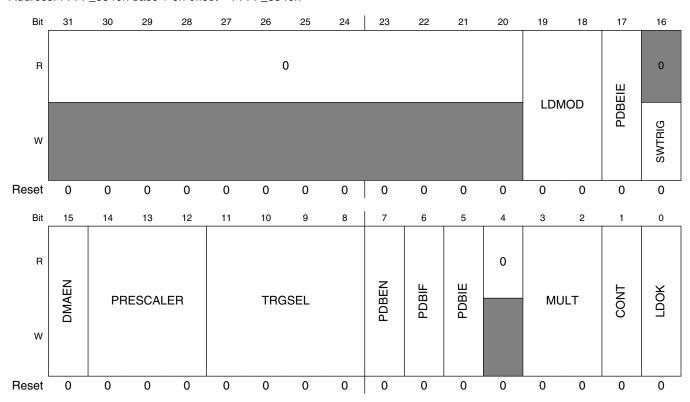

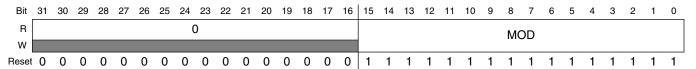

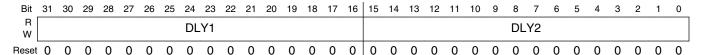

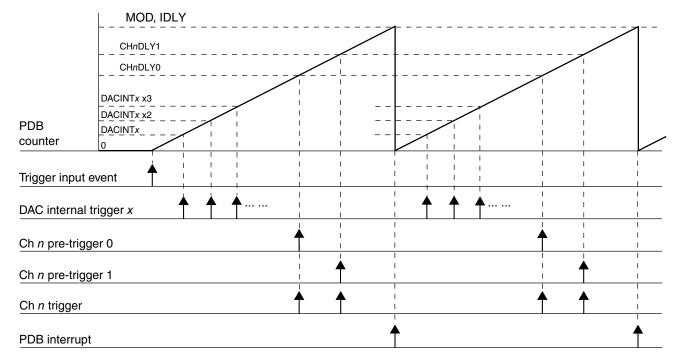

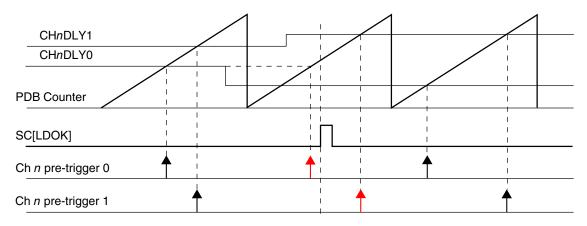

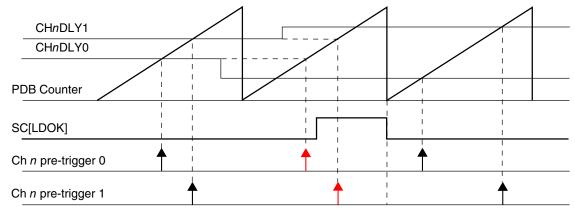

|                | 3.9.1  | Programm   | mable Delay Block (PDB) Configuration               | 110  |

|                |        | 3.9.1.1    | Module register width and serialization of accesses | 110  |

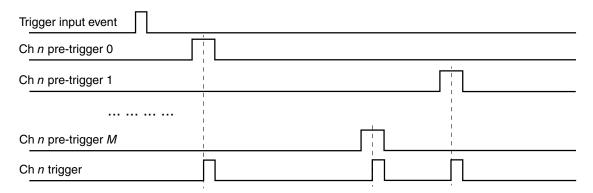

|                |        | 3.9.1.2    | PDB Overview                                        | 111  |

|                |        | 3.9.1.3    | PDB instantiation                                   | 111  |

|                |        | 3.9.1.4    | PDB Module Interconnections                         | 111  |

|                |        | 3.9.1.5    | PDB acknowledgement connections                     | 112  |

|                |        |            |                                                     |      |

| Sec  | tion nu | ımber          | Title                                                  | Page |  |

|------|---------|----------------|--------------------------------------------------------|------|--|

|      |         | 3.9.1.6        | PDB Interval Trigger Connection to DAC                 | 112  |  |

|      |         | 3.9.1.7        | DAC External Trigger Input Connection.                 | 112  |  |

|      |         | 3.9.1.8        | Pulse-Out Connection.                                  | 112  |  |

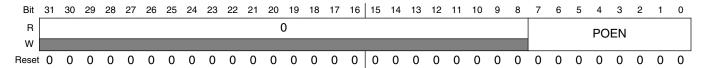

|      |         | 3.9.1.9        | Pulse-Out Enable Register Implementation               | 112  |  |

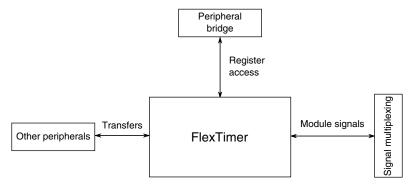

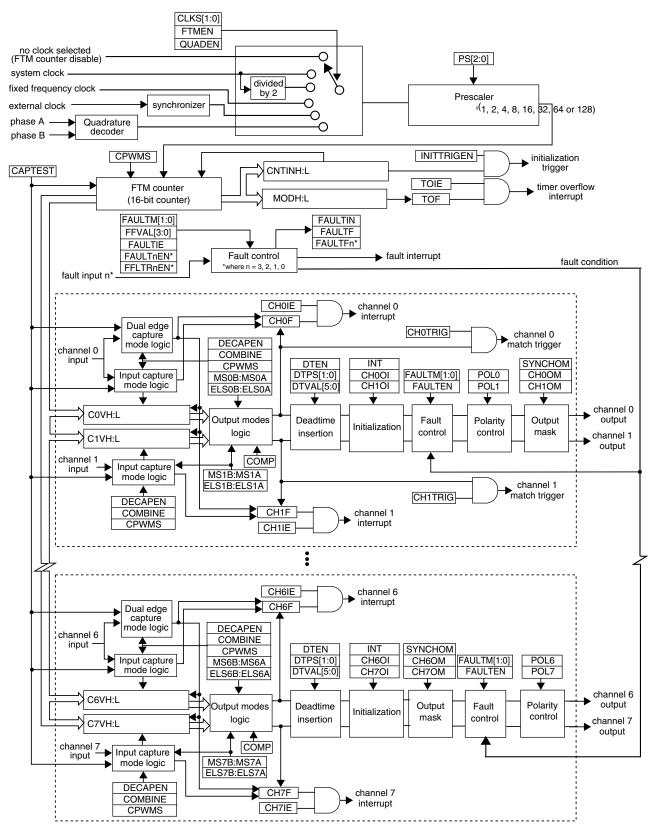

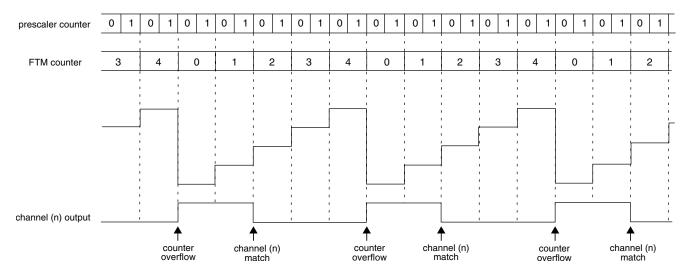

|      | 3.9.2   | FlexTimer      | r (FTM) Configuration                                  | 113  |  |

|      |         | 3.9.2.1        | FTM overview                                           | 113  |  |

|      |         | 3.9.2.2        | FTM instantiation information.                         | 113  |  |

|      |         | 3.9.2.3        | FTM external clock options.                            | 115  |  |

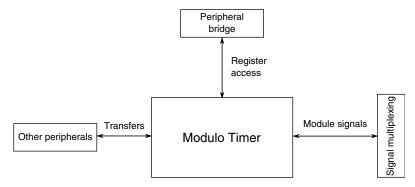

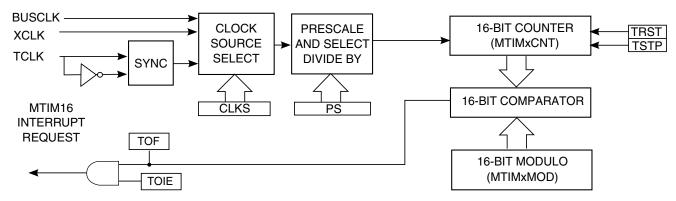

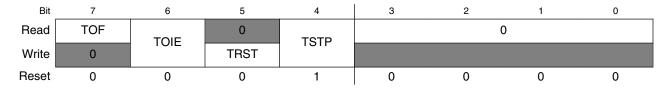

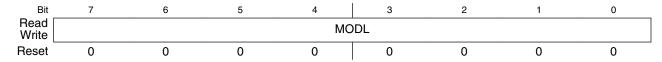

|      | 3.9.3   | Modulo T       | imer (MTIM) Configuration                              | 115  |  |

|      |         | 3.9.3.1        | MTIM overview                                          | 115  |  |

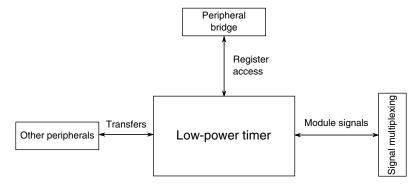

|      | 3.9.4   | Low Powe       | er Timer (LPTMR) Configuration                         | 116  |  |

|      |         | 3.9.4.1        | LPTMR overview                                         | 116  |  |

|      |         | 3.9.4.2        | LPTMR pin connections                                  | 117  |  |

|      |         | 3.9.4.3        | LPTMR clock options                                    | 117  |  |

|      |         | 3.9.4.4        | LPTMR register reset                                   | 117  |  |

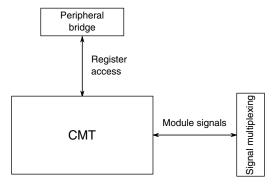

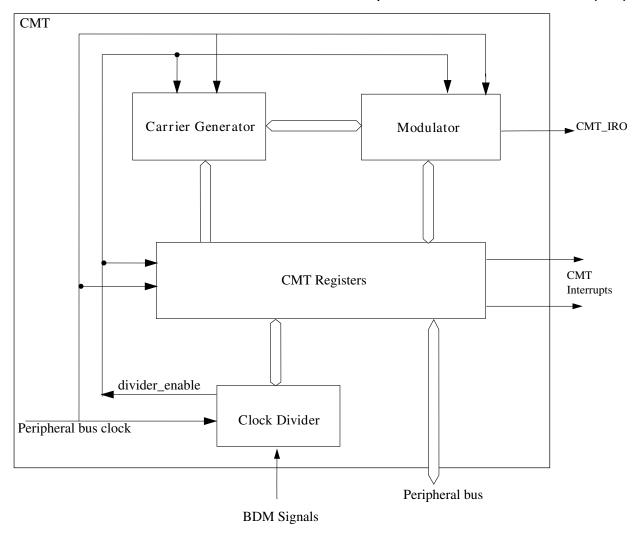

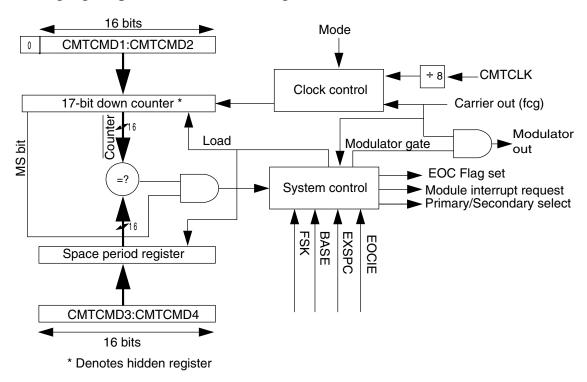

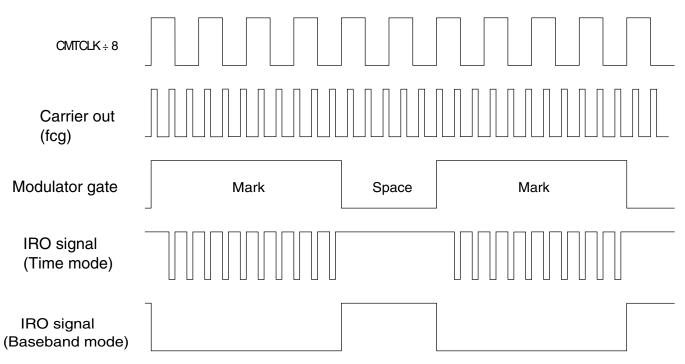

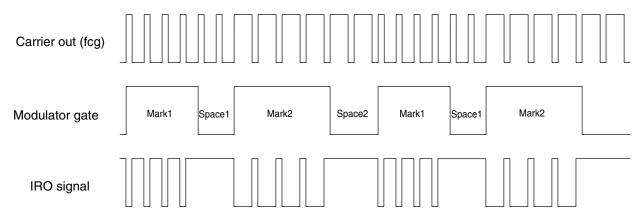

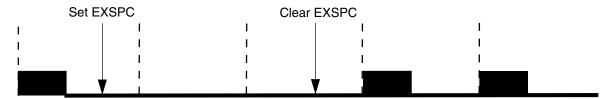

|      | 3.9.5   | Carrier Mo     | odulator Transmitter (CMT) Configuration               | 118  |  |

|      |         | 3.9.5.1        | CMT instantiation information                          | 118  |  |

|      |         | 3.9.5.2        | CMT IRO drive strength                                 | 118  |  |

| 3.10 | Commu   | inication into | erfaces                                                | 119  |  |

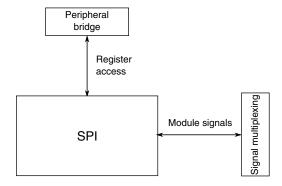

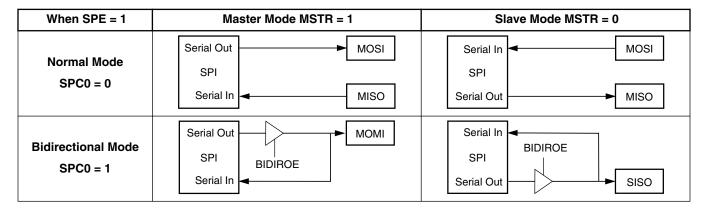

|      | 3.10.1  | Serial Peri    | ipheral Interface (SPI) Configuration                  | 119  |  |

|      |         | 3.10.1.1       | Number and instantiation of SPI modules                | 119  |  |

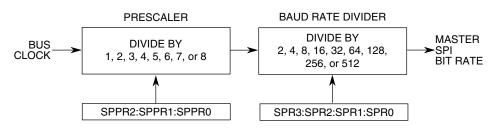

|      |         | 3.10.1.2       | SPI baud rate                                          | 119  |  |

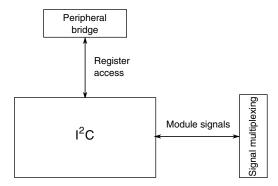

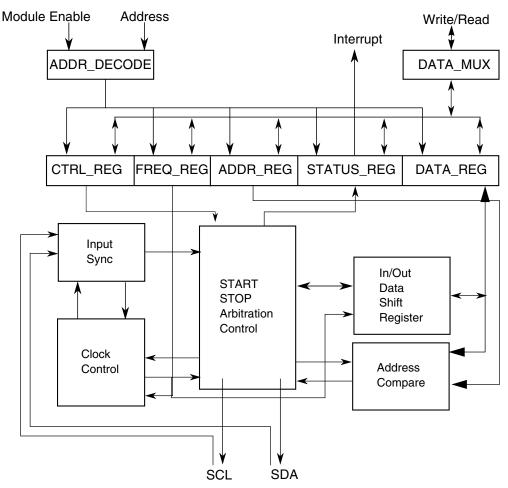

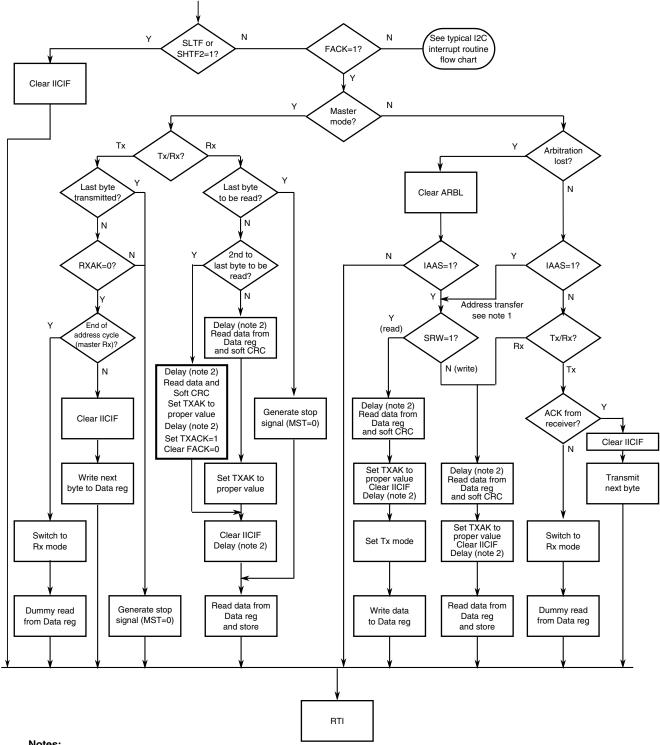

|      | 3.10.2  | Inter-Integ    | grated Circuit (I2C) Configuration                     | 120  |  |

|      |         | 3.10.2.1       | Number of I2C modules                                  | 120  |  |

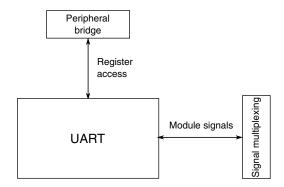

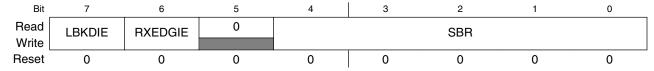

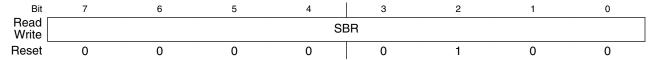

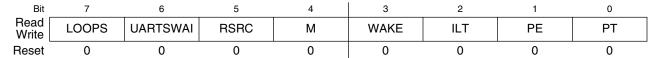

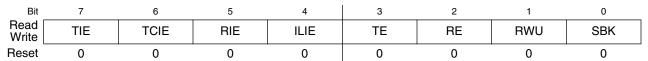

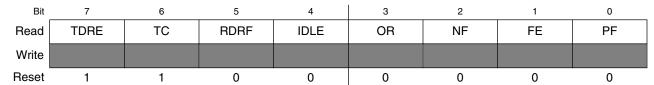

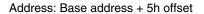

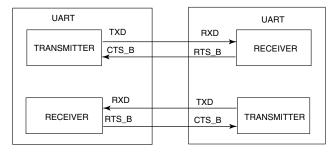

|      | 3.10.3  | Universal      | Asynchronous Receiver/Transmitter (UART) Configuration | 121  |  |

|      |         | 3.10.3.1       | UART instances                                         | 121  |  |

|      |         | 3.10.3.2       | UART wakeup                                            | 121  |  |

|      |         | 3.10.3.3       | UART support for opto-isolated interface               | 121  |  |

| Sec  | tion nu | ımber                          | Title                                                  | Page |

|------|---------|--------------------------------|--------------------------------------------------------|------|

| 3.11 | Human   | Human-machine interfaces (HMI) |                                                        |      |

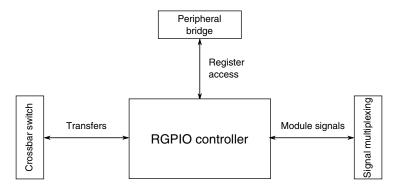

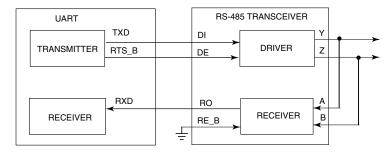

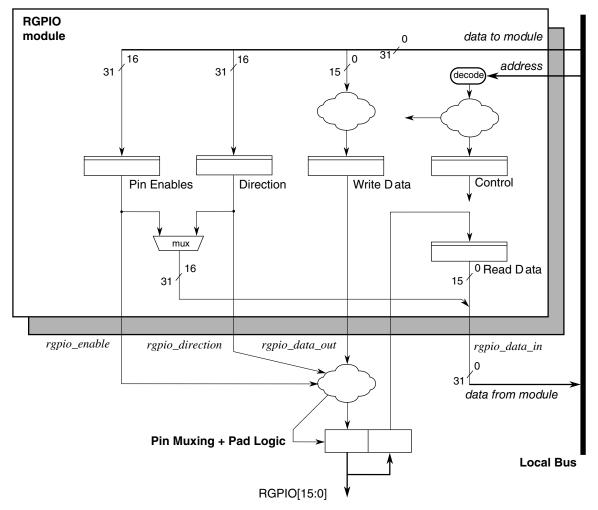

|      | 3.11.1  | Rapid GP                       | IO (RGPIO) Configuration                               | 122  |

|      |         | 3.11.1.1                       | Number of available RGPIO pins.                        | 122  |

|      |         | 3.11.1.2                       | RGPIO clock gating                                     | 123  |

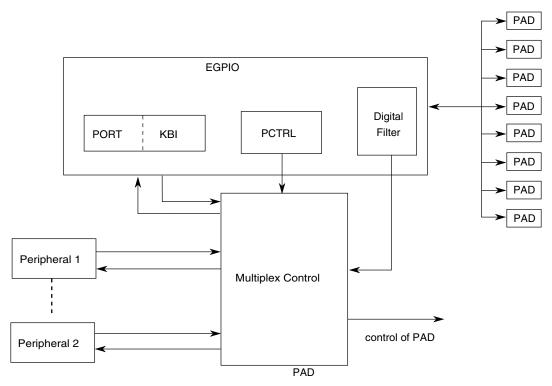

|      | 3.11.2  | Enhanced                       | GPIO (EGPIO) Configuration                             | 123  |

|      |         | 3.11.2.1                       | Instantiation Information.                             | 123  |

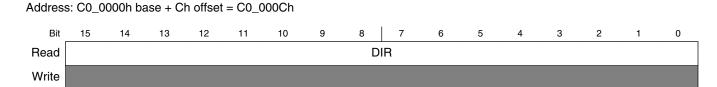

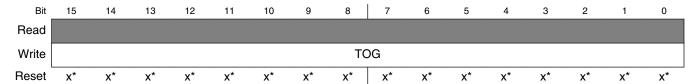

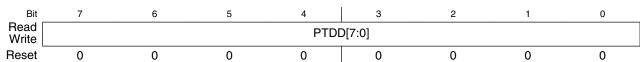

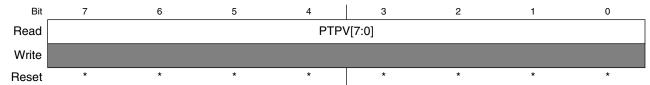

|      |         | 3.11.2.2                       | EGPIO registers                                        | 124  |

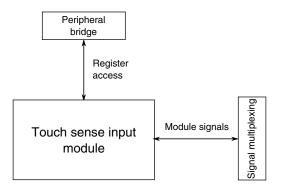

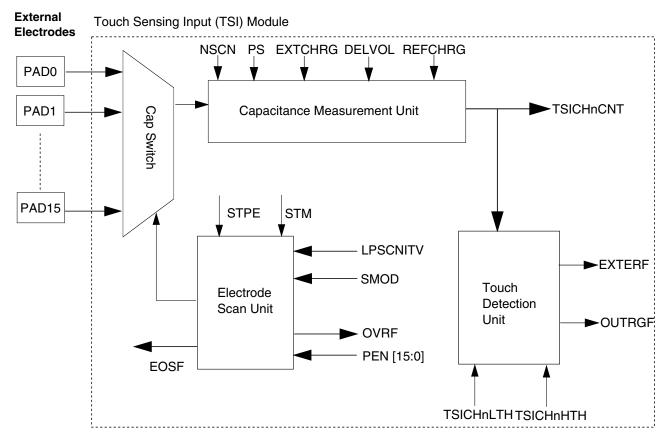

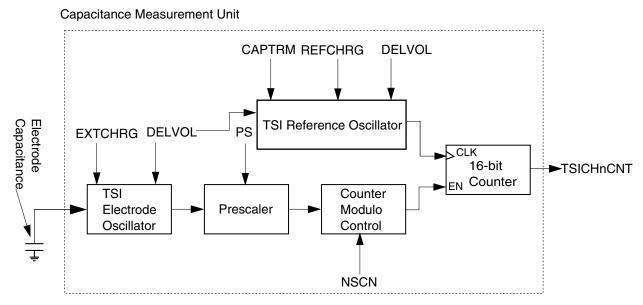

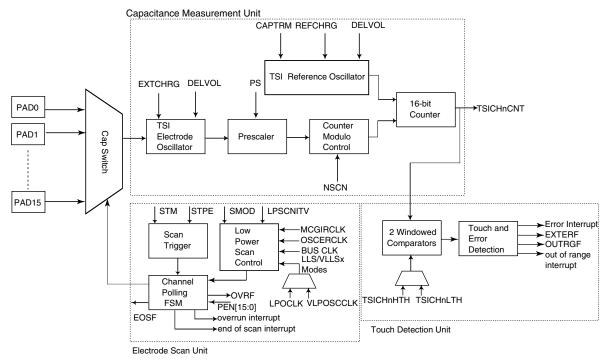

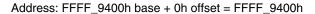

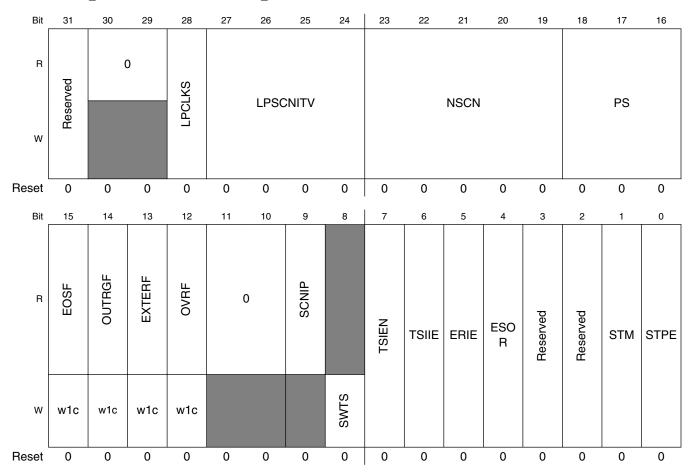

|      | 3.11.3  | Touch Ser                      | nse Input (TSI) Configuration                          | 124  |

|      |         | 3.11.3.1                       | Module register width and serialization of accesses    | 125  |

|      |         | 3.11.3.2                       | Number and instantiation of inputs.                    | 125  |

|      |         | 3.11.3.3                       | TSI clock names.                                       | 125  |

|      |         | 3.11.3.4                       | TSI module functionality in MCU operation modes        | 125  |

|      |         | 3.11.3.5                       | TSI Interrupts                                         | 126  |

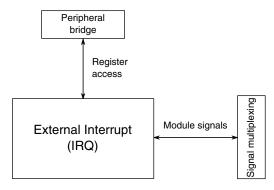

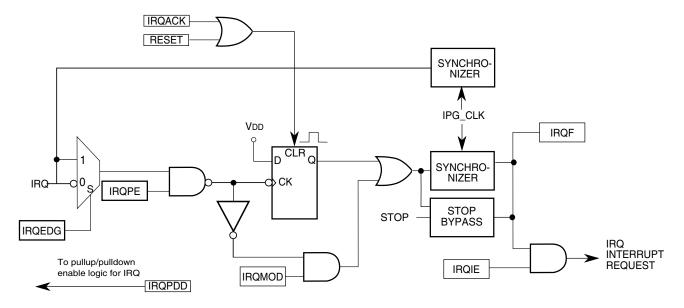

|      | 3.11.4  | External I                     | nterrupt (IRQ) Module Configuration                    | 126  |

|      |         |                                | Chapter 4<br>Memory Map                                |      |

| 4.1  | System  | Memory M                       | [ap                                                    | 129  |

| 4.2  | Read-at | fter-write se                  | quence and required serialization of memory operations | 134  |

|      |         |                                | Chapter 5 Clock Distribution                           |      |

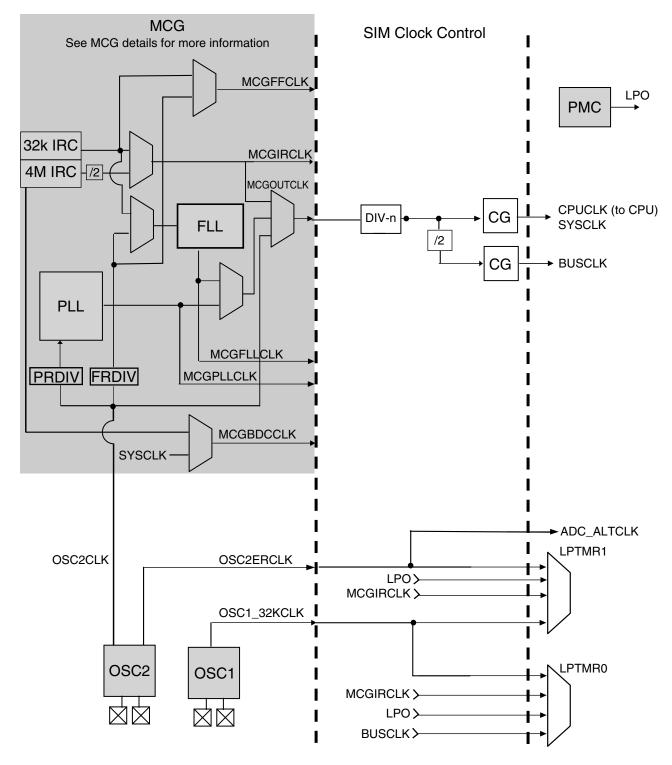

| 5.1  | Introdu | ction                          |                                                        | 135  |

| 5.2  | Clock d | listribution                   |                                                        | 135  |

|      | 5.2.1   | High-Leve                      | el device clocking diagram                             | 135  |

|      | 5.2.2   | Device Cl                      | ock Summary                                            | 136  |

|      | 5.2.3   | Architectu                     | ıre                                                    | 138  |

|      | 5.2.4   | Clock divi                     | ider requirements                                      | 138  |

|      | 5.2.5   | Clock gati                     | ing                                                    | 139  |

|      | 5.2.6   | Module cl                      | locks                                                  | 139  |

|      |         | 5.2.6.1                        | VLPR Mode Clocking                                     | 140  |

|      |         |                                |                                                        |      |

| Sect | Section number     |             | Title                                            | Page |

|------|--------------------|-------------|--------------------------------------------------|------|

|      |                    | 5.2.6.2     | UART Clocking                                    | 140  |

|      |                    | 5.2.6.3     | PMC's LPO clock                                  | 141  |

|      |                    |             | Chapter 6<br>Reset and Boot                      |      |

| 6.1  | Reset              |             |                                                  | 143  |

|      | 6.1.1              | MCU rese    | et sources                                       | 143  |

|      |                    | 6.1.1.1     | Power-on reset (POR)                             | 144  |

|      |                    | 6.1.1.2     | External RESET pin (PIN)                         | 144  |

|      |                    | 6.1.1.3     | COP watchdog (WDOG) timer                        | 145  |

|      |                    | 6.1.1.4     | Illegal opcode detect (ILOP)                     | 145  |

|      |                    | 6.1.1.5     | Illegal address detect (ILAD)                    | 145  |

|      |                    | 6.1.1.6     | Multipurpose Clock Generator loss of clock (LOC) | 146  |

|      |                    | 6.1.1.7     | Low voltage detect (LVD)                         | 146  |

|      |                    | 6.1.1.8     | Low leakage wakeup (WAKEUP)                      | 146  |

|      |                    | 6.1.1.9     | Stop mode acknowledge error (SACKERR)            | 147  |

|      |                    | 6.1.1.10    | Background debug forced reset (BDFR)             | 147  |

|      | 6.1.2              | Reset Pin   |                                                  | 147  |

|      | 6.1.3              | MCU Res     | sets                                             | 148  |

|      |                    | 6.1.3.1     | POR Only                                         | 148  |

|      |                    | 6.1.3.2     | Chip POR not VLLS                                | 148  |

|      |                    | 6.1.3.3     | Chip POR                                         | 148  |

|      |                    | 6.1.3.4     | Chip Reset not VLLS                              | 148  |

|      |                    | 6.1.3.5     | Early Chip Reset                                 | 148  |

|      |                    | 6.1.3.6     | Chip Reset                                       | 149  |

| 6.2  | Boot               |             |                                                  | 149  |

|      | 6.2.1 Boot sources |             | 149                                              |      |

|      | 6.2.2              | Boot option | ons                                              | 149  |

|      | 6.2.3              | FOPT boo    | ot options                                       | 150  |

|      | 6.2.4              | Boot sequ   | ience                                            | 151  |

|      |                    |             |                                                  |      |

MCF51QM128 Reference Manual, Rev. 4, 08/2012

| Sec  | tion nu | mber Title                                  | Page |  |

|------|---------|---------------------------------------------|------|--|

|      | 9.7.2   | System Modules                              | 183  |  |

|      | 9.7.3   | Clock Modules.                              | 184  |  |

|      | 9.7.4   | Memories and Memory Interfaces.             | 184  |  |

|      | 9.7.5   | Analog                                      | 186  |  |

|      | 9.7.6   | Timer Modules                               | 186  |  |

|      | 9.7.7   | Communication Interfaces                    | 188  |  |

|      | 9.7.8   | Human-Machine Interfaces (HMI)              | 189  |  |

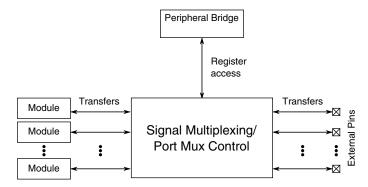

|      |         | Chapter 10<br>Port Mux Control              |      |  |

| 10.1 | Port Mu | x Control                                   | 191  |  |

| 10.2 | Memory  | Map and Registers                           | 191  |  |

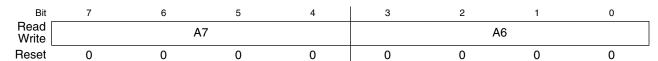

|      | 10.2.1  | Port A Pin Function 1 Register (MXC_PTAPF1) | 192  |  |

|      | 10.2.2  | Port A Pin Function 2 Register (MXC_PTAPF2) | 193  |  |

|      | 10.2.3  | Port A Pin Function 3 Register (MXC_PTAPF3) | 194  |  |

|      | 10.2.4  | Port A Pin Function 4 Register (MXC_PTAPF4) | 194  |  |

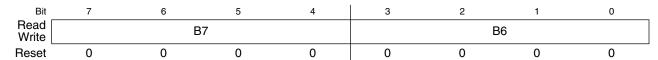

|      | 10.2.5  | Port B Pin Function 1 Register (MXC_PTBPF1) | 195  |  |

|      | 10.2.6  | Port B Pin Function 2 Register (MXC_PTBPF2) | 196  |  |

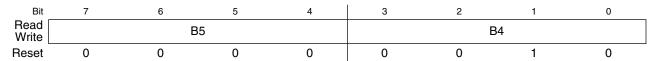

|      | 10.2.7  | Port B Pin Function 3 Register (MXC_PTBPF3) | 197  |  |

|      | 10.2.8  | Port B Pin Function 4 Register (MXC_PTBPF4) | 197  |  |

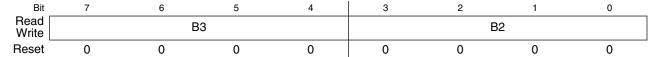

|      | 10.2.9  | Port C Pin Function 1 Register (MXC_PTCPF1) | 198  |  |

|      | 10.2.10 | Port C Pin Function 2 Register (MXC_PTCPF2) | 199  |  |

|      | 10.2.11 | Port C Pin Function 3 Register (MXC_PTCPF3) | 200  |  |

|      | 10.2.12 | Port C Pin Function 4 Register (MXC_PTCPF4) | 200  |  |

|      | 10.2.13 | Port D Pin Function 1 Register (MXC_PTDPF1) | 201  |  |

|      | 10.2.14 | Port D Pin Function 2 Register (MXC_PTDPF2) | 202  |  |

|      | 10.2.15 | Port D Pin Function 3 Register (MXC_PTDPF3) | 203  |  |

|      | 10.2.16 | Port D Pin Function 4 Register (MXC_PTDPF4) | 203  |  |

|      | 10.2.17 | Port E Pin Function 1 Register (MXC_PTEPF1) | 204  |  |

|      | 10.2.18 | Port E Pin Function 2 Register (MXC_PTEPF2) | 205  |  |

| Sect | ion nu                          | mber                                               | Title                                            | Page |  |

|------|---------------------------------|----------------------------------------------------|--------------------------------------------------|------|--|

|      | 10.2.19                         | Port E Pin                                         | n Function 3 Register (MXC_PTEPF3)               | 206  |  |

|      | 10.2.20                         | Port E Pin                                         | Function 4 Register (MXC_PTEPF4)                 | 206  |  |

|      | 10.2.21                         | Port F Pin                                         | Function 1 Register (MXC_PTFPF1)                 | 207  |  |

|      | 10.2.22                         | Port F Pin                                         | Function 2 Register (MXC_PTFPF2)                 | 208  |  |

|      | 10.2.23                         | Port F Pin                                         | Function 3 Register (MXC_PTFPF3)                 | 209  |  |

|      | 10.2.24                         | Port F Pin                                         | Function 4 Register (MXC_PTFPF4)                 | 209  |  |

|      |                                 |                                                    | Chapter 11<br>Core                               |      |  |

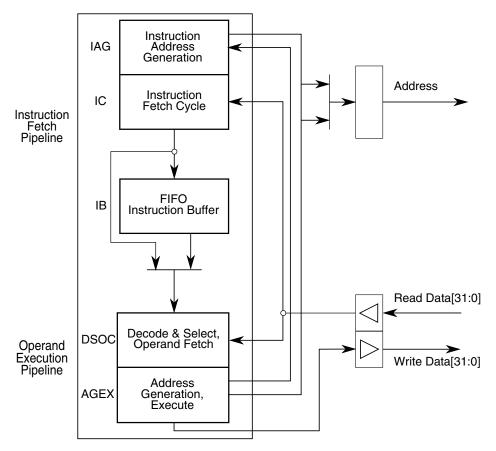

| 11.1 | Introduc                        | ction                                              |                                                  | 211  |  |

|      | 11.1.1                          | Overview.                                          |                                                  | 211  |  |

| 11.2 | Memory Map/Register Description |                                                    |                                                  | 213  |  |

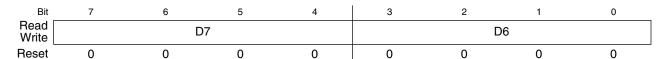

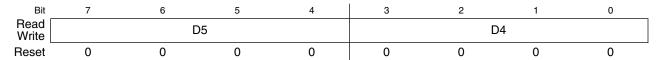

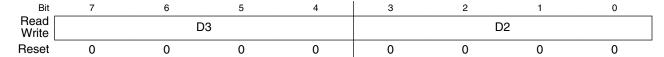

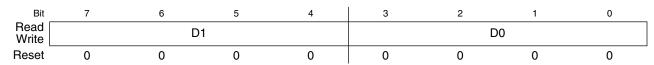

|      | 11.2.1                          | 2.1 Data registers (D0–D7)                         |                                                  |      |  |

|      | 11.2.2                          | Address re                                         | 216                                              |      |  |

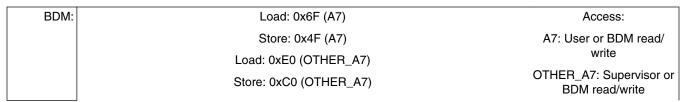

|      | 11.2.3                          | 3 Supervisor/user stack pointers (A7 and OTHER_A7) |                                                  |      |  |

|      | 11.2.4                          | Condition                                          | 218                                              |      |  |

|      | 11.2.5                          | Program c                                          | counter (PC)                                     | 219  |  |

|      | 11.2.6                          | Vector bas                                         | se register (VBR)                                | 219  |  |

|      | 11.2.7                          | CPU confi                                          | iguration register (CPUCR)                       | 220  |  |

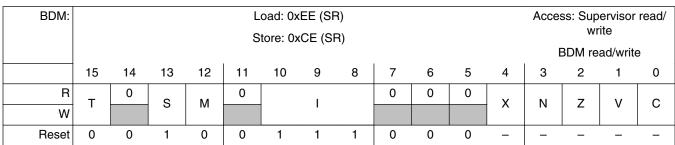

|      | 11.2.8                          | Status regi                                        | ister (SR)                                       | 223  |  |

| 11.3 | Functional Description.         |                                                    |                                                  | 224  |  |

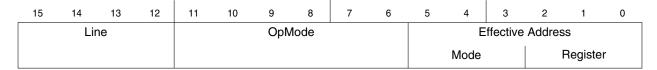

|      | 11.3.1                          | Instruction                                        | n Set Architecture                               | 224  |  |

|      | 11.3.2                          | Exception                                          | Processing Overview                              | 225  |  |

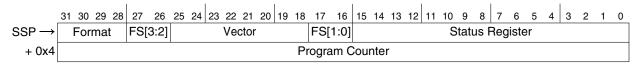

|      |                                 | 11.3.2.1                                           | Exception Stack Frame Definition                 | 228  |  |

|      |                                 | 11.3.2.2                                           | S08 and ColdFire Exception Processing Comparison | 229  |  |

|      | 11.3.3                          | Processor                                          | Exceptions                                       | 230  |  |

|      |                                 | 11.3.3.1                                           | Access Error Exception                           | 230  |  |

|      |                                 | 11.3.3.2                                           | Address Error Exception.                         | 231  |  |

|      |                                 | 11.3.3.3                                           | Illegal Instruction Exception.                   | 232  |  |

|      |                                 | 11.3.3.4                                           | Divide-By-Zero                                   | 233  |  |

| Sect | tion nu | ımber       | ber Title                                           |     |  |

|------|---------|-------------|-----------------------------------------------------|-----|--|

|      |         | 11.3.3.5    | Privilege Violation                                 | 233 |  |

|      |         | 11.3.3.6    | Trace Exception.                                    | 234 |  |

|      |         | 11.3.3.7    | Unimplemented Line-A Opcode                         | 234 |  |

|      |         | 11.3.3.8    | Unimplemented Line-F Opcode.                        | 235 |  |

|      |         | 11.3.3.9    | Debug Interrupt                                     | 235 |  |

|      |         | 11.3.3.10   | RTE and Format Error Exception                      | 235 |  |

|      |         | 11.3.3.11   | TRAP Instruction Exception.                         | 236 |  |

|      |         | 11.3.3.12   | Unsupported Instruction Exception.                  | 236 |  |

|      |         | 11.3.3.13   | Interrupt Exception                                 | 236 |  |

|      |         | 11.3.3.14   | Fault-on-Fault Halt.                                | 236 |  |

|      |         | 11.3.3.15   | Reset Exception.                                    | 237 |  |

|      | 11.3.4  | Instruction | n Execution Timing                                  | 240 |  |

|      |         | 11.3.4.1    | Timing Assumptions.                                 | 240 |  |

|      |         | 11.3.4.2    | MOVE Instruction Execution Times.                   | 241 |  |

|      |         | 11.3.4.3    | Standard One Operand Instruction Execution Times    | 242 |  |

|      |         | 11.3.4.4    | Standard Two Operand Instruction Execution Times    | 243 |  |

|      |         | 11.3.4.5    | Miscellaneous Instruction Execution Times.          | 244 |  |

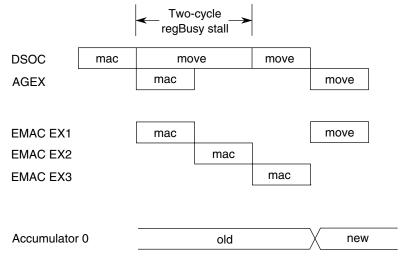

|      |         | 11.3.4.6    | EMAC Instruction Execution Times                    | 245 |  |

|      |         | 11.3.4.7    | Branch Instruction Execution Times                  | 247 |  |

|      |         |             | Chapter 12 Enhanced Multiply-Accumulate Unit (EMAC) |     |  |

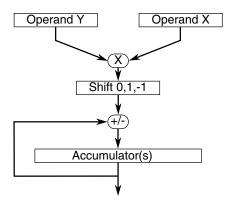

| 12.1 | Introdu | ction       |                                                     | 249 |  |

|      | 12.1.1  | Overview.   |                                                     | 249 |  |

|      |         | 12.1.1.1    | Introduction to the MAC                             | 250 |  |

| 12.2 | Memor   | y Map/Regis | ster Definition                                     | 251 |  |

|      | 12.2.1  | MAC Statu   | us Register (MACSR)                                 | 252 |  |

|      | 12.2.2  | Mask Regi   | ister (MASK)                                        | 254 |  |

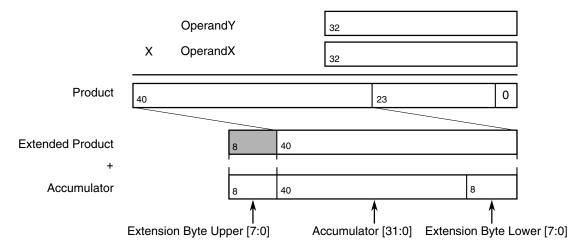

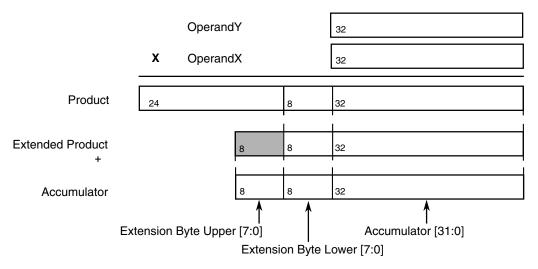

|      | 12.2.3  | Accumulat   | tor Registers (ACC0-3)                              | 256 |  |

|      | 12.2.4  | Accumulat   | tor Extension Registers (ACCext01, ACCext23)        | 257 |  |

| Sec  | tion nu  | mber                  | Title                                           | Page |

|------|----------|-----------------------|-------------------------------------------------|------|

| 12.3 | Function | nal Descript          | tion                                            | 258  |

|      | 12.3.1   | Fractional            | Operation Mode                                  | 260  |

|      |          | 12.3.1.1              | Rounding                                        | 261  |

|      |          | 12.3.1.2              | Saving and Restoring the EMAC Programming Model | 262  |

|      |          | 12.3.1.3              | MULS/MULU                                       | 263  |

|      |          | 12.3.1.4              | Scale Factor in MAC or MSAC Instructions        | 263  |

|      | 12.3.2   | EMAC Ins              | struction Set Summary                           | 263  |

|      | 12.3.3   | EMAC Ins              | struction Execution Times                       | 264  |

|      | 12.3.4   | Data Repr             | resentation                                     | 265  |

|      | 12.3.5   | MAC Opc               | codes                                           | 265  |

|      |          |                       | Chapter 13 System Integration Module (SIM)      |      |

| 13.1 | Introduc | ction                 |                                                 | 271  |

| 13.2 | Memory   | y Map and F           | Registers                                       | 271  |

|      | 13.2.1   | System O <sub>1</sub> | ptions Register 1 (SIM_SOPT1)                   | 273  |

|      | 13.2.2   | System O <sub>1</sub> | ptions Register 2 (SIM_SOPT2)                   | 274  |

|      | 13.2.3   | System O <sub>1</sub> | ptions Register 3 (SIM_SOPT3)                   | 275  |

|      | 13.2.4   | System O <sub>1</sub> | ptions Register 4 (SIM_SOPT4)                   | 276  |

|      | 13.2.5   | System O <sub>1</sub> | ptions Register 5 (SIM_SOPT5)                   | 277  |

|      | 13.2.6   | System O <sub>1</sub> | ptions Register 6 (SIM_SOPT6)                   | 277  |

|      | 13.2.7   | System O <sub>1</sub> | ptions Register 7 (SIM_SOPT7)                   | 278  |

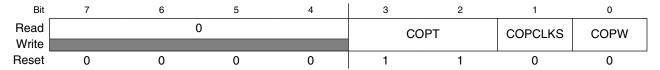

|      | 13.2.8   | COP Cont              | trol Register (SIM_COPC)                        | 279  |

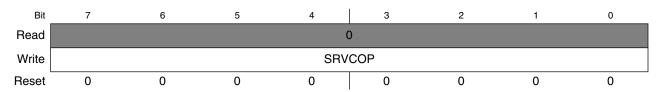

|      | 13.2.9   | Service Co            | OP Register (SIM_SRVCOP)                        | 280  |

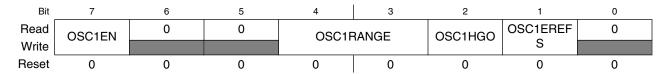

|      | 13.2.10  | Oscillator            | 1 Control Register (SIM_OSC1)                   | 281  |

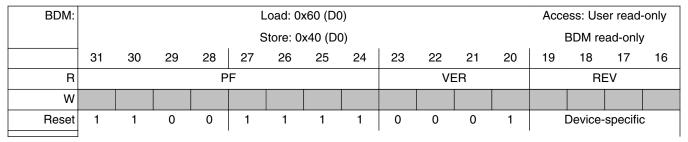

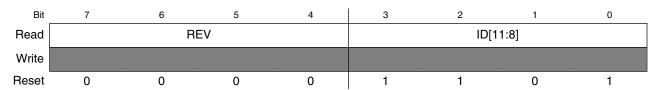

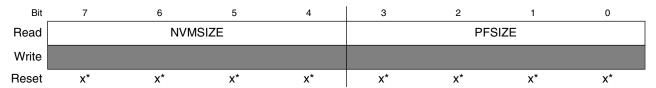

|      | 13.2.11  | Device Ide            | entification High Register (SIM_SDIDH)          | 282  |

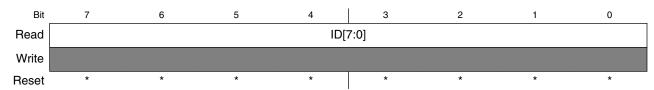

|      | 13.2.12  | Device Ide            | entification Low Register (SIM_SDIDL)           | 282  |

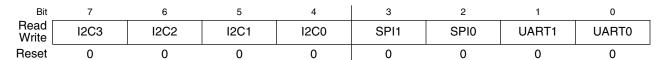

|      | 13.2.13  | Clock Gat             | te Control Register 1 (SIM_SCGC1)               | 283  |

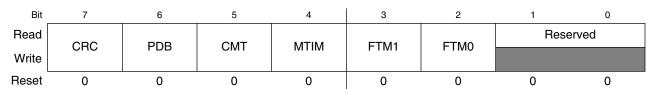

|      | 13.2.14  | Clock Gat             | te Control Register 2 (SIM_SCGC2)               | 284  |

|      | 13.2.15  | Clock Gat             | te Control Register 3 (SIM_SCGC3)               | 285  |

| Sec  | tion nu  | mber Title                                  | Page |

|------|----------|---------------------------------------------|------|

|      | 13.2.16  | Clock Gate Control Register 4 (SIM_SCGC4)   | 286  |

|      | 13.2.17  | Clock Gate Control Register 5 (SIM_SCGC5)   | 287  |

|      | 13.2.18  | Clock Gate Control Register 6 (SIM_SCGC6)   | 288  |

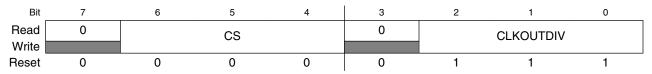

|      | 13.2.19  | Clockout Register (SIM_CLKOUT)              | 289  |

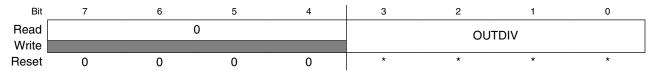

|      | 13.2.20  | Clock Divider 0 Register (SIM_CLKDIV0)      | 290  |

|      | 13.2.21  | Flash Configuration Register (SIM_SPCR)     | 291  |

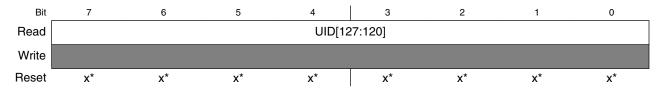

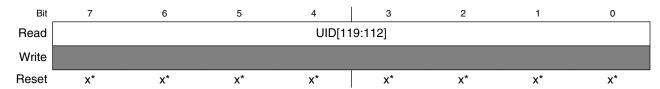

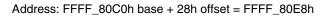

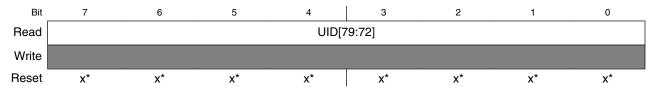

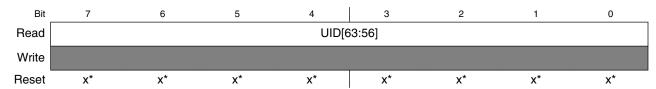

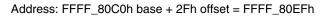

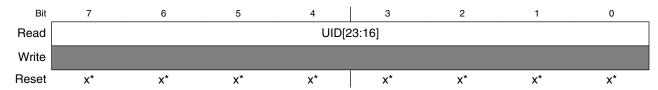

|      | 13.2.22  | Unique Identification Register (SIM_UIDH3)  | 292  |

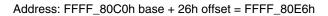

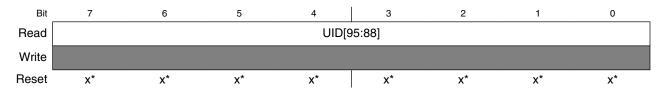

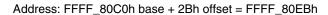

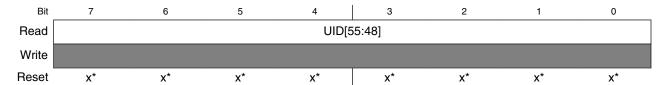

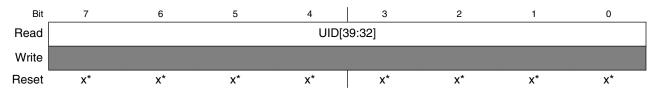

|      | 13.2.23  | Unique Identification Register (SIM_UIDH2)  | 293  |

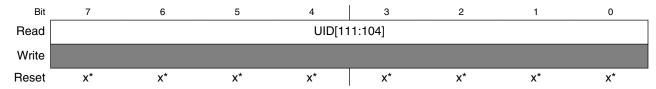

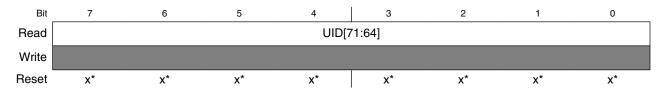

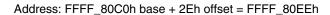

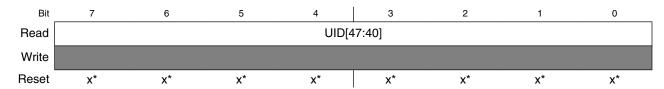

|      | 13.2.24  | Unique Identification Register (SIM_UIDH1)  | 294  |

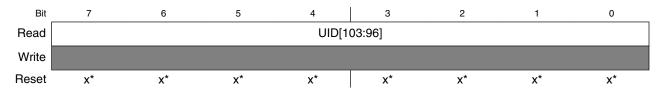

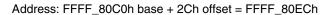

|      | 13.2.25  | Unique Identification Register (SIM_UIDH0)  | 294  |

|      | 13.2.26  | Unique Identification Register (SIM_UIDMH3) | 295  |

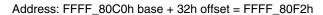

|      | 13.2.27  | Unique Identification Register (SIM_UIDMH2) | 296  |

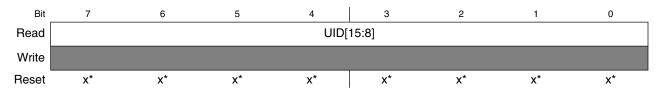

|      | 13.2.28  | Unique Identification Register (SIM_UIDMH1) | 296  |

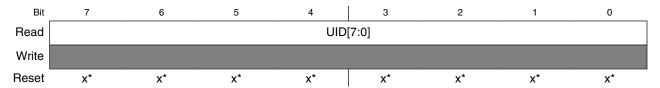

|      | 13.2.29  | Unique Identification Register (SIM_UIDMH0) | 297  |

|      | 13.2.30  | Unique Identification Register (SIM_UIDML3) | 298  |

|      | 13.2.31  | Unique Identification Register (SIM_UIDML2) | 298  |

|      | 13.2.32  | Unique Identification Register (SIM_UIDML1) | 299  |

|      | 13.2.33  | Unique Identification Register (SIM_UIDML0) | 300  |

|      | 13.2.34  | Unique Identification Register (SIM_UIDL3)  | 300  |

|      | 13.2.35  | Unique Identification Register (SIM_UIDL2)  | 301  |

|      | 13.2.36  | Unique Identification Register (SIM_UIDL1)  | 302  |

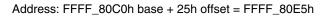

|      | 13.2.37  | Unique Identification Register (SIM_UIDL0)  | 302  |

|      |          | Chapter 14<br>Crossbar Switch               |      |

| 14.1 | Introduc | ction                                       | 305  |

|      | 14.1.1   | Features.                                   | 305  |

| 14.2 | Memory   | y Map / Register Definition                 | 306  |

| 14.3 | Function | nal Description                             | 306  |

|      | 14.3.1   | General operation                           | 306  |

|      |          |                                             |      |

| Sec  | Section number             |              | Title                                              | Page |

|------|----------------------------|--------------|----------------------------------------------------|------|

|      | 14.3.2                     | Arbitratio   | on                                                 | 307  |

|      |                            | 14.3.2.1     | Arbitration During Undefined Length Bursts         | 307  |

|      |                            | 14.3.2.2     | Fixed-priority operation.                          | 307  |

|      |                            | 14.3.2.3     | Round-robin priority operation                     | 308  |

|      |                            | 14.3.2.4     | Priority Elevation.                                | 308  |

| 14.4 | Initializ                  | ation/applic | cation information                                 | 309  |

|      |                            |              | Chapter 15<br>Interrupt Controller (INTC)          |      |

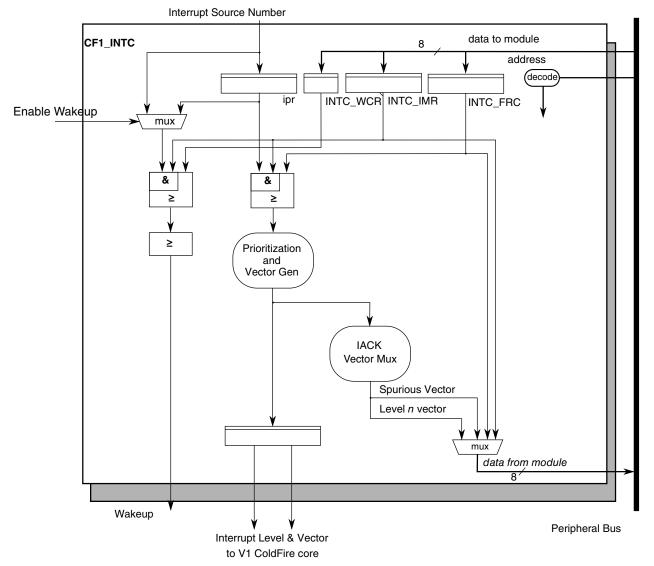

| 15.1 | Introduc                   | ction        |                                                    | 311  |

|      | 15.1.1                     | Overview     | /                                                  | 312  |

|      | 15.1.2                     | Features     |                                                    | 315  |

|      | 15.1.3                     | Modes of     | Operation                                          | 316  |

| 15.2 | Externa                    | l Signal De  | escription                                         | 316  |

| 15.3 | Interrup                   | t Request L  | Level and Priority Assignments                     | 316  |

| 15.4 | Memor                      | y Map and l  | Registers                                          | 317  |

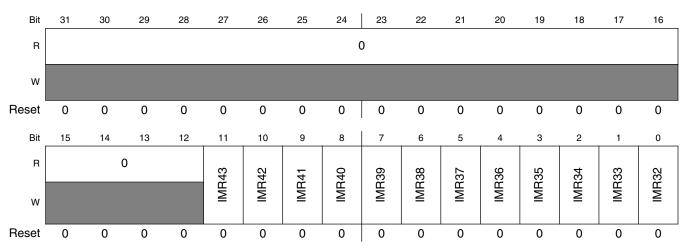

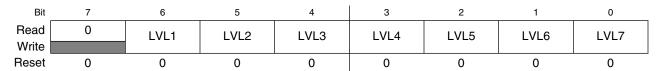

|      | 15.4.1                     | Interrupt l  | Mask Register High (INTC_IMRH)                     | 318  |

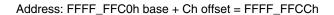

|      | 15.4.2                     | Interrupt l  | Mask Register Low (INTC_IMRL)                      | 320  |

|      | 15.4.3                     | Force Inte   | errupt Register (INTC_FRC)                         | 324  |

|      | 15.4.4                     | INTC Pro     | ogrammable Level 6 Priority Registers (INTC_PL6Pn) | 325  |

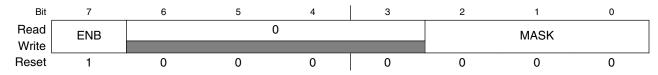

|      | 15.4.5                     | INTC Wa      | akeup Control Register (INTC_WCR)                  | 326  |

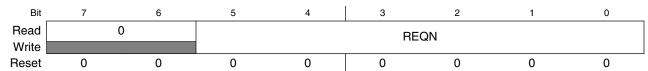

|      | 15.4.6                     | Set Interru  | rupt Mask Register (INTC_SIMR)                     | 327  |

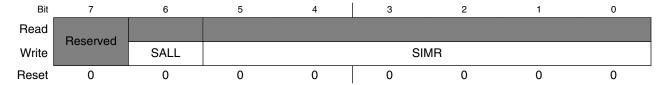

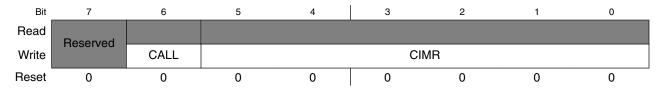

|      | 15.4.7                     | Clear Inte   | errupt Mask Register (INTC_CIMR)                   | 328  |

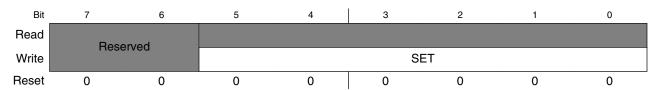

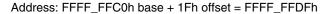

|      | 15.4.8                     | INTC Set     | t Interrupt Force Register (INTC_SFRC)             | 329  |

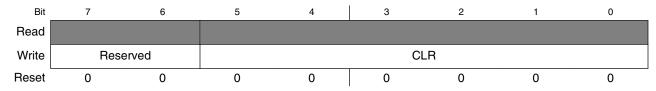

|      | 15.4.9                     | INTC Cle     | ear Interrupt Force Register (INTC_CFRC)           | 330  |

|      | 15.4.10                    | INTC Sof     | ftware IACK Register (INTC_SWIACK)                 | 331  |

|      | 15.4.11                    | INTC Lev     | vel-n IACK Registers (INTC_LVLnIACK)               | 331  |

| 15.5 | Functio                    | nal Descrip  | otion                                              |      |

|      | 15.5.1                     | Handling     | of Non-Maskable Level 7 Interrupt Requests         | 332  |

| 15.6 | Initialization Information |              |                                                    |      |

| Sect | tion nu  | imber Title                                   | Page |

|------|----------|-----------------------------------------------|------|

| 15.7 | Applica  | tion Information                              | 333  |

|      | 15.7.1   | Emulation of the HCS08's 1-Level IRQ Handling | 333  |

|      | 15.7.2   | Using INTC_PL6P{7,6} Registers                | 334  |

|      | 15.7.3   | More on Software IACKs                        | 335  |

|      |          | Chapter 16<br>Low Leakage Wakeup Unit (LLWU)  |      |

| 16.1 | Introduc | ction                                         | 339  |

|      | 16.1.1   | Features                                      | 339  |

|      | 16.1.2   | Modes of operation                            | 340  |

|      |          | 16.1.2.1 LLS mode                             | 340  |

|      |          | 16.1.2.2 VLLS modes                           | 340  |

|      |          | 16.1.2.3 Non-low leakage modes                | 340  |

|      |          | 16.1.2.4 Debug mode                           | 341  |

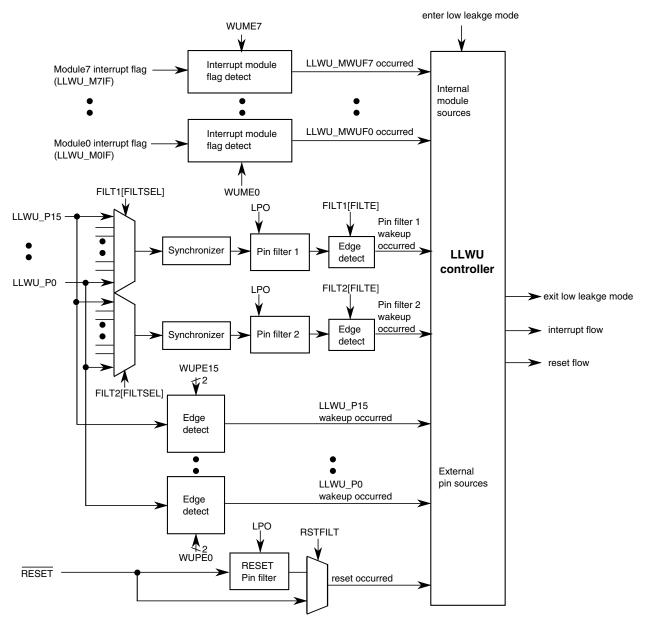

|      | 16.1.3   | Block diagram                                 | 341  |

| 16.2 | LLWU     | signal descriptions.                          | 342  |

| 16.3 | Memor    | y map/register definition                     | 343  |

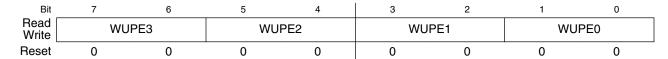

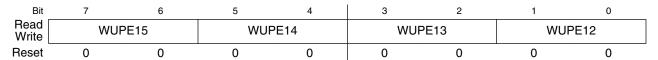

|      | 16.3.1   | LLWU Pin Enable 1 register (LLWU_PE1)         | 344  |

|      | 16.3.2   | LLWU Pin Enable 2 register (LLWU_PE2)         | 345  |

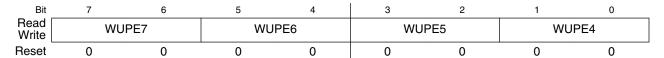

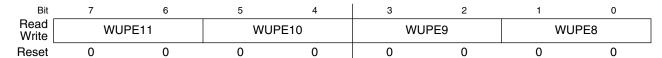

|      | 16.3.3   | LLWU Pin Enable 3 register (LLWU_PE3)         | 346  |

|      | 16.3.4   | LLWU Pin Enable 4 register (LLWU_PE4)         | 347  |

|      | 16.3.5   | LLWU Module Enable register (LLWU_ME)         | 348  |

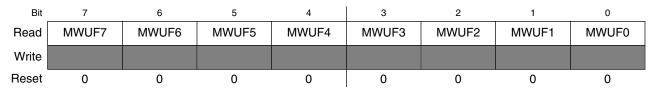

|      | 16.3.6   | LLWU Flag 1 register (LLWU_F1)                | 350  |

|      | 16.3.7   | LLWU Flag 2 register (LLWU_F2)                | 351  |

|      | 16.3.8   | LLWU Flag 3 register (LLWU_F3)                | 353  |

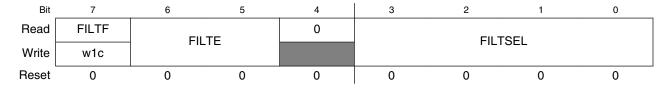

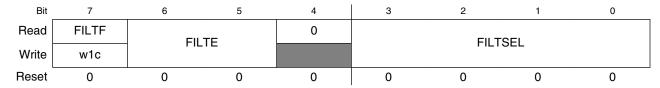

|      | 16.3.9   | LLWU Pin Filter 1 register (LLWU_FILT1)       | 355  |

|      | 16.3.10  | LLWU Pin Filter 2 register (LLWU_FILT2)       | 356  |

|      | 16.3.11  | LLWU Reset Enable register (LLWU_RST)         | 357  |

| 16.4 | Functio  | nal description                               | 358  |

|      | 16.4.1   | LLS mode                                      | 358  |

| Sec  | tion nu | ımber           | Title                                    | Page |

|------|---------|-----------------|------------------------------------------|------|

|      | 16.4.2  | VLLS mod        | les                                      | 358  |

|      | 16.4.3  | Initialization  | on                                       |      |

|      |         |                 | Chapter 17<br>Reset Control Module (RCM) |      |

| 17.1 | Introdu | ction           |                                          | 361  |

| 17.2 | Reset m | nemory map      | and register descriptions                | 361  |

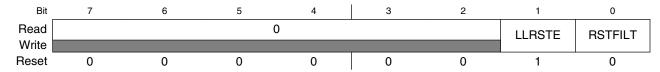

|      | 17.2.1  | System Re       | set Status Register 0 (RCM_SRS0)         | 361  |

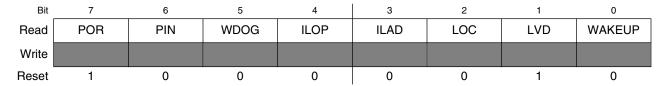

|      | 17.2.2  | System Re       | set Status Register 1 (RCM_SRS1)         | 363  |

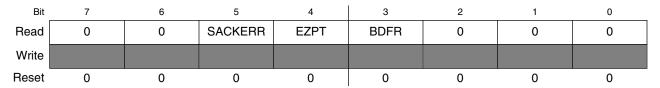

|      | 17.2.3  | Reset Pin I     | Filter Control register (RCM_RPFC)       | 364  |

|      | 17.2.4  | Reset Pin I     | Filter Width register (RCM_RPFW)         |      |

|      | 17.2.5  | Mode Regi       | ister (RCM_MR)                           | 367  |

|      |         |                 | Chapter 18 System Mode Controller (SMC)  |      |

| 18.1 | Introdu | ction           |                                          | 369  |

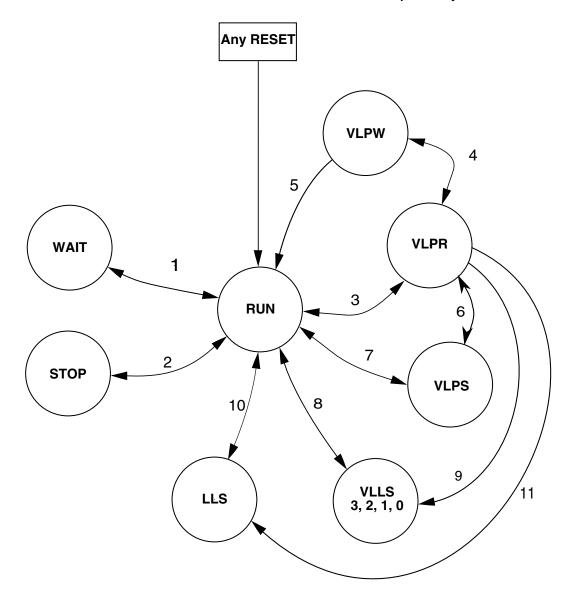

| 18.2 | Modes   | of operation.   |                                          | 369  |

| 18.3 | Memor   | y map and re    | gister descriptions                      | 371  |

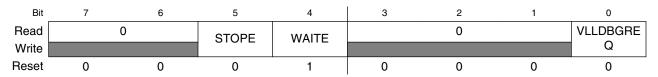

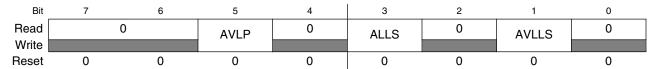

|      | 18.3.1  | Power Mod       | de Protection register (SMC_PMPROT)      | 371  |

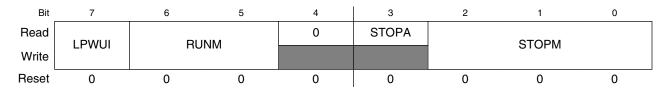

|      | 18.3.2  | Power Mod       | de Control register (SMC_PMCTRL)         | 372  |

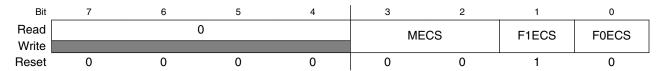

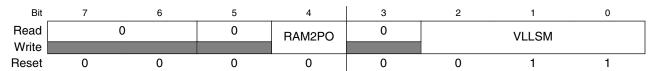

|      | 18.3.3  | VLLS Con        | trol register (SMC_VLLSCTRL)             |      |

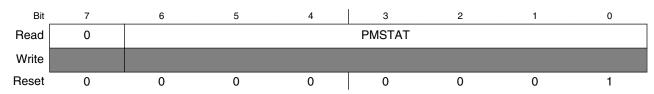

|      | 18.3.4  | Power Mod       | de Status register (SMC_PMSTAT)          | 375  |

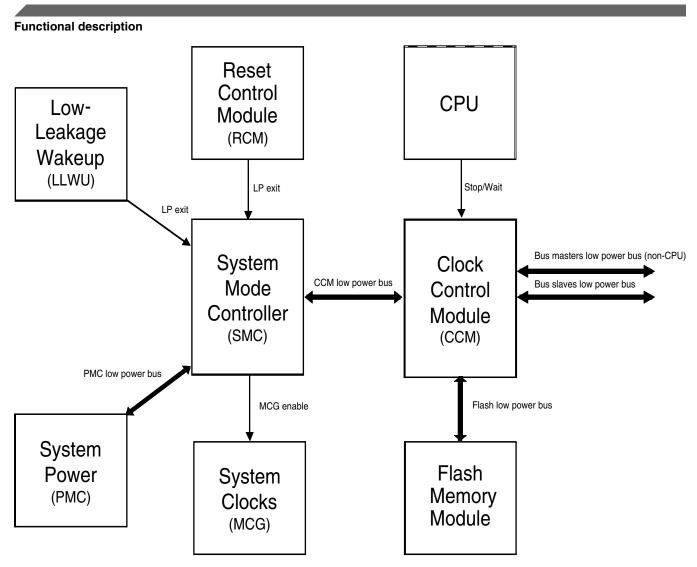

| 18.4 | Functio | nal description | on                                       | 376  |

|      | 18.4.1  | Power mod       | le transitions                           | 376  |

|      | 18.4.2  | Power mod       | le entry/exit sequencing                 | 379  |

|      |         | 18.4.2.1        | Stop mode entry sequence                 | 380  |

|      |         | 18.4.2.2        | Stop mode exit sequence                  | 381  |

|      |         | 18.4.2.3        | Aborted stop mode entry                  | 381  |

|      |         | 18.4.2.4        | Transition to wait modes                 | 381  |

|      |         | 18.4.2.5        | Transition from stop modes to Debug mode | 381  |

| Sec  | Section number |               | TITIE                                                 | Page |

|------|----------------|---------------|-------------------------------------------------------|------|

|      | 18.4.3         | Run mode      | es                                                    | 381  |

|      |                | 18.4.3.1      | RUN mode                                              | 382  |

|      |                | 18.4.3.2      | Very-Low Power Run (VLPR) mode                        | 382  |

|      |                | 18.4.3.3      | BDM in Run and VLPR Mode                              | 383  |

|      | 18.4.4         | Wait mod      | es                                                    | 383  |

|      |                | 18.4.4.1      | WAIT mode                                             | 383  |

|      |                | 18.4.4.2      | Very-Low-Power Wait (VLPW) mode                       | 384  |

|      |                | 18.4.4.3      | BDM in Wait and VLPW Mode                             | 384  |

|      | 18.4.5         | Stop mode     | es                                                    | 385  |

|      |                | 18.4.5.1      | STOP mode                                             | 385  |

|      |                | 18.4.5.2      | Very-Low-Power Stop (VLPS) mode                       | 386  |

|      |                | 18.4.5.3      | BDM in Stop and VLPS Modes                            | 386  |

|      |                | 18.4.5.4      | Low-Leakage Stop (LLS) mode                           | 387  |

|      |                | 18.4.5.5      | Very-Low-Leakage Stop (VLLSx) modes                   | 387  |

|      |                | 18.4.5.6      | BDM in LLS and VLLSx Modes                            | 388  |

|      |                |               | Chapter 19 Power Management Controller (PMC)          |      |

| 19.1 | Introdu        | ction         | · · · · · · · · · · · · · · · · · · ·                 | 389  |

| 19.2 | Feature        | S             |                                                       | 389  |

| 19.3 | Low-vo         | oltage detect | t (LVD) system                                        | 389  |

|      | 19.3.1         | LVD reset     | t operation                                           | 390  |

|      | 19.3.2         | LVD inter     | rrupt operation                                       | 390  |

|      | 19.3.3         | Low-volta     | age warning (LVW) interrupt operation                 | 390  |

| 19.4 | I/O rete       | ntion         |                                                       | 391  |

| 19.5 | Memor          | y map and r   | register descriptions                                 | 391  |

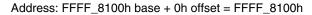

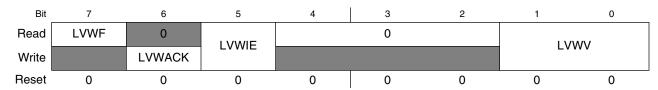

|      | 19.5.1         | Low Volta     | age Detect Status And Control 1 register (PMC_LVDSC1) | 391  |

|      | 19.5.2         | Low Volta     | age Detect Status And Control 2 register (PMC_LVDSC2) | 393  |

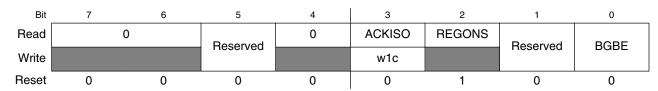

|      | 19.5.3         | Regulator     | Status And Control register (PMC_REGSC)               | 394  |

|      |                |               |                                                       |      |

21.4.5

### Chapter 22 Multipurpose Clock Generator (MCG)

| 22.1 | 1 Introduction |                                                       |     |  |  |

|------|----------------|-------------------------------------------------------|-----|--|--|

|      | 22.1.1         | Features                                              | 423 |  |  |

|      | 22.1.2         | Modes of Operation                                    | 427 |  |  |

| 22.2 | External       | l Signal Description                                  | 427 |  |  |

| 22.3 | Memory         | y Map/Register Definition                             | 427 |  |  |

|      | 22.3.1         | MCG Control 1 Register (MCG_C1)                       | 427 |  |  |

|      | 22.3.2         | MCG Control 2 Register (MCG_C2)                       | 429 |  |  |

|      | 22.3.3         | MCG Control 3 Register (MCG_C3)                       | 430 |  |  |

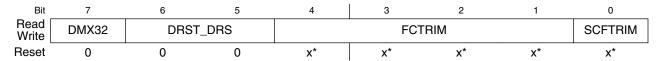

|      | 22.3.4         | MCG Control 4 Register (MCG_C4)                       | 430 |  |  |

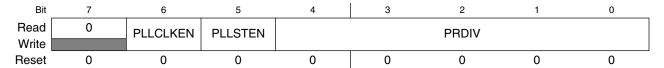

|      | 22.3.5         | MCG Control 5 Register (MCG_C5)                       | 432 |  |  |

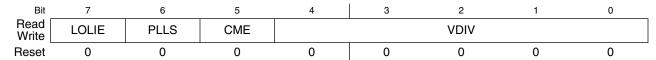

|      | 22.3.6         | MCG Control 6 Register (MCG_C6)                       | 433 |  |  |

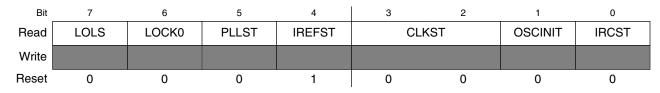

|      | 22.3.7         | MCG Status Register (MCG_S)                           | 434 |  |  |

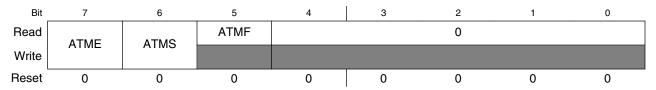

|      | 22.3.8         | MCG Auto Trim Control Register (MCG_ATC)              | 436 |  |  |

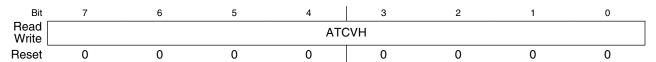

|      | 22.3.9         | MCG Auto Trim Compare Value High Register (MCG_ATCVH) | 436 |  |  |

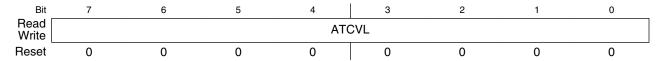

|      | 22.3.10        | MCG Auto Trim Compare Value Low Register (MCG_ATCVL)  | 437 |  |  |

| 22.4 | Function       | nal Description                                       | 437 |  |  |

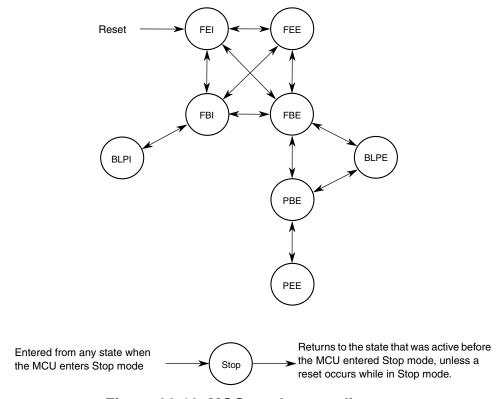

|      | 22.4.1         | MCG mode state diagram.                               | 437 |  |  |

|      |                | 22.4.1.1 MCG modes of operation                       | 438 |  |  |

|      |                | 22.4.1.2 MCG mode switching                           | 441 |  |  |

|      | 22.4.2         | Low Power Bit Usage                                   | 442 |  |  |

|      | 22.4.3         | MCG Internal Reference Clocks                         | 442 |  |  |

|      |                | 22.4.3.1 MCG Internal Reference Clock                 | 442 |  |  |

|      | 22.4.4         | External Reference Clock                              | 443 |  |  |

|      | 22.4.5         | MCG Fixed frequency clock                             | 443 |  |  |

|      | 22.4.6         | MCG Background Debug Controller Clock                 | 443 |  |  |

|      | 22.4.7         | MCG PLL clock                                         | 444 |  |  |

|      | 22.4.8         | MCG Auto TRIM (ATM)                                   | 444 |  |  |

| Sec  | tion nu   | ımber          | Title                                                                                          | Page |

|------|-----------|----------------|------------------------------------------------------------------------------------------------|------|

| 22.5 | Initializ | cation / App   | lication information                                                                           | 445  |

|      | 22.5.1    | MCG mod        | dule initialization sequence                                                                   | 445  |

|      |           | 22.5.1.1       | Initializing the MCG                                                                           | 445  |

|      | 22.5.2    | Using a 32     | 2.768 kHz reference                                                                            | 447  |

|      | 22.5.3    | MCG mod        | de switching                                                                                   | 448  |

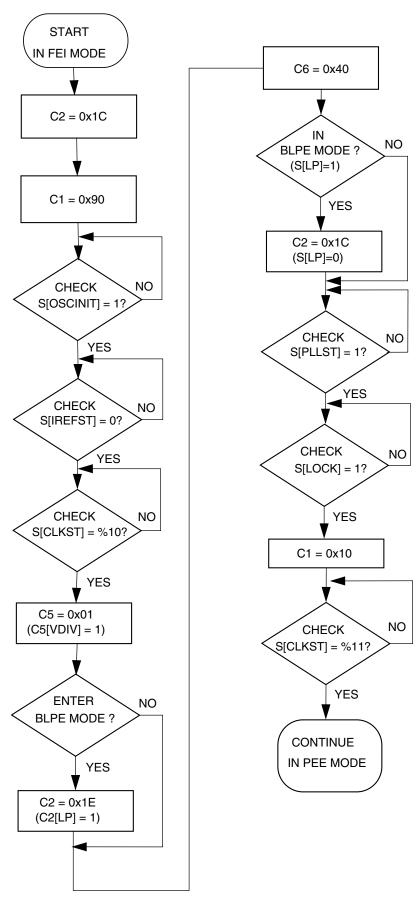

|      |           | 22.5.3.1       | Example 1: Moving from FEI to PEE mode: External Crystal = 4 MHz, MCGOUTCLK frequency = 48 MHz |      |

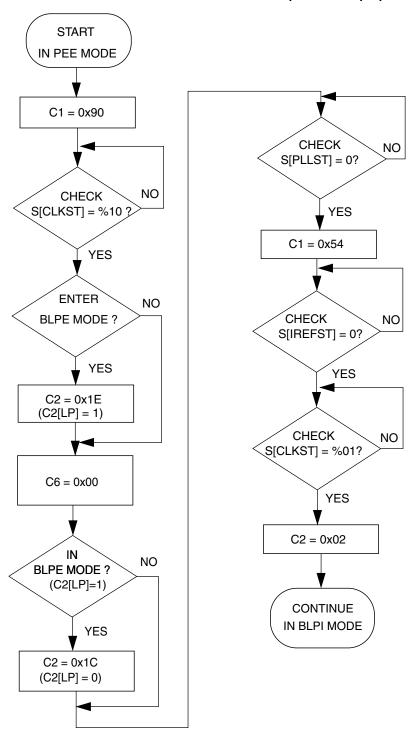

|      |           | 22.5.3.2       | Example 2: Moving from PEE to BLPI mode: MCGOUTCLK frequency =32 kHz                           | 453  |

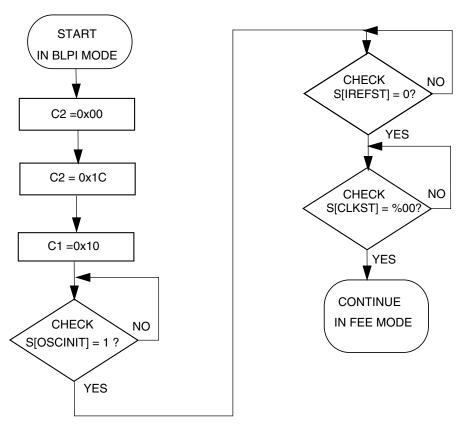

|      |           | 22.5.3.3       | Example 3: Moving from BLPI to FEE mode                                                        | 455  |

|      |           |                | Chapter 23<br>Oscillator (OSC)                                                                 |      |

| 23.1 | Introdu   | ction          |                                                                                                | 459  |

| 23.2 | Feature   | s and Mode     | s                                                                                              | 459  |

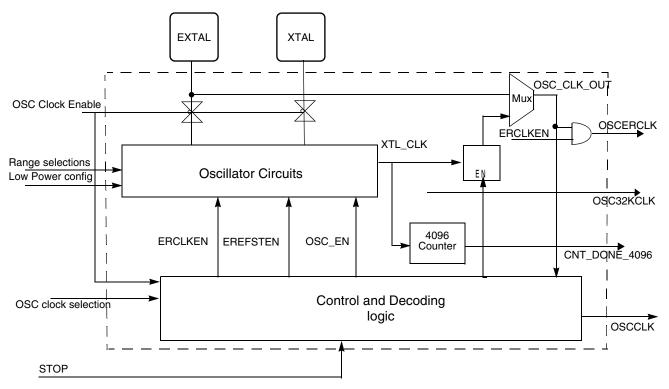

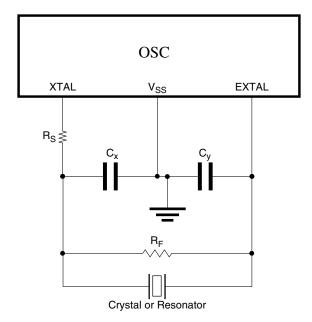

| 23.3 | Block I   | Diagram        |                                                                                                | 460  |

| 23.4 | OSC Si    | gnal Descri    | ptions                                                                                         | 460  |

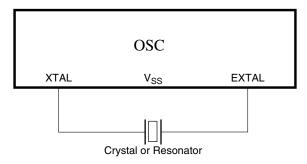

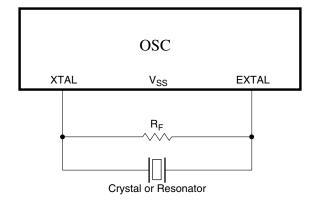

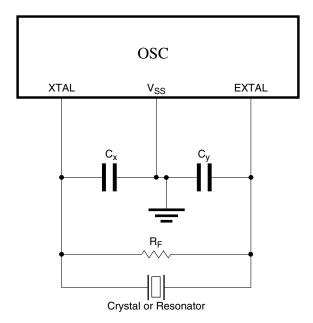

| 23.5 | Externa   | ıl Crystal / F | Resonator Connections.                                                                         | 461  |

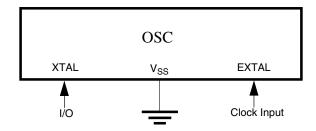

| 23.6 | Externa   | ıl Clock Cor   | nnections                                                                                      | 463  |

| 23.7 | Memor     | y Map/Regi     | ster Definitions                                                                               | 463  |

|      | 23.7.1    | OSC Men        | nory Map/Register Definition                                                                   | 464  |

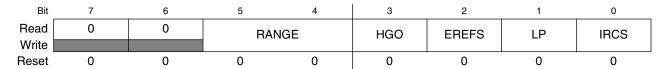

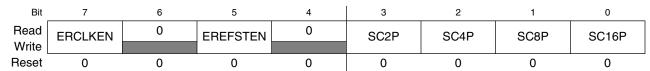

|      |           | 23.71.1        | OSC Control Register (OSCx_CR)                                                                 | 464  |

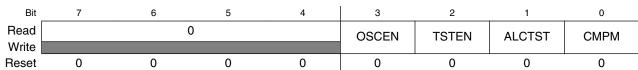

|      |           | 23.71.2        | OSC Test Control Register (OSCx_TSTCTR)                                                        | 465  |

| 23.8 | Functio   | nal Descrip    | tion                                                                                           | 466  |

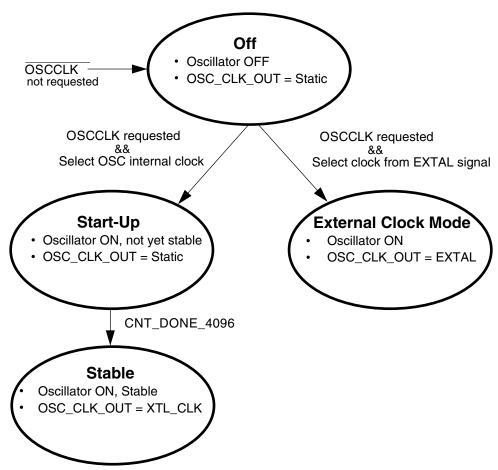

|      | 23.8.1    | OSC Mod        | lule States                                                                                    | 466  |

|      |           | 23.8.1.1       | Off                                                                                            | 467  |

|      |           | 23.8.1.2       | Oscillator Start-Up                                                                            | 467  |

|      |           | 23.8.1.3       | Oscillator Stable                                                                              | 468  |

|      |           | 23.8.1.4       | External Clock Mode                                                                            | 468  |

|      | 23.8.2    | OSC Mod        | lule Modes                                                                                     | 468  |

|      |           | 23.8.2.1       | Low-Frequency, High-Gain Mode                                                                  | 469  |

| Sect  | ion nu   | ımber          | Title                                    | Page |

|-------|----------|----------------|------------------------------------------|------|

|       |          | 23.8.2.2       | Low-Frequency, Low-Power Mode            | 469  |

|       |          | 23.8.2.3       | High-Frequency, High-Gain Mode           | 469  |

|       |          | 23.8.2.4       | High-Frequency, Low-Power Mode           | 470  |

|       | 23.8.3   | Counter        |                                          | 470  |

|       | 23.8.4   | Reference      | e Clock Pin Requirements                 | 470  |

| 23.9  | Reset    |                |                                          | 470  |

| 23.10 | Low Po   | ower Modes     | Operation                                | 471  |

| 23.11 | Interrup | ots            |                                          | 471  |

|       |          |                | Chapter 24 Flash Memory Controller (FMC) |      |

| 24.1  | Introdu  | ction          |                                          | 473  |

|       | 24.1.1   | Overview       | ·                                        | 473  |

|       | 24.1.2   | Features       |                                          | 473  |

| 24.2  | Modes    | of operation   | 1                                        | 474  |

| 24.3  | Externa  | ıl signal desc | cription                                 | 474  |

| 24.4  | Memor    | y map and r    | register descriptions                    | 474  |

| 24.5  | Functio  | nal descript   | tion                                     | 475  |

|       |          |                | Chapter 25<br>Flash Memory Module (FTFL) |      |

| 25.1  | Introdu  | ction          |                                          | 477  |

|       | 25.1.1   | Features       |                                          | 478  |

|       |          | 25.1.1.1       | Program Flash Memory Features            | 478  |

|       |          | 25.1.1.2       | FlexNVM Memory Features                  | 478  |

|       |          | 25.1.1.3       | FlexRAM Features                         | 478  |

|       |          | 25.1.1.4       | Other Flash Memory Module Features       | 479  |

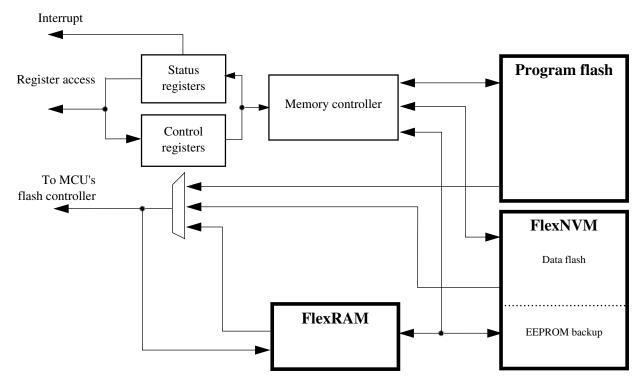

|       | 25.1.2   | Block Dia      | agram                                    | 479  |

|       | 25.1.3   | Glossary       |                                          | 480  |

| 25.2  | Externa  | l Signal Des   | scription                                | 482  |

| Section number |         | ımber       | Title                                               | Page |

|----------------|---------|-------------|-----------------------------------------------------|------|

| 25.3           | Memor   | y Map and I | Registers                                           | 482  |

|                | 25.3.1  | Flash Con   | figuration Field Description                        | 483  |

|                | 25.3.2  | Program I   | Flash IFR Map                                       | 483  |

|                |         | 25.3.2.1    | Program Once Field.                                 | 483  |

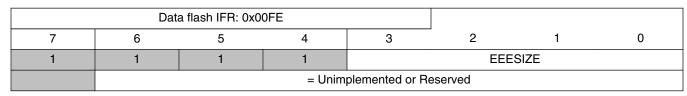

|                | 25.3.3  | Data Flash  | h IFR Map                                           | 484  |

|                |         | 25.3.3.1    | EEPROM Data Set Size                                | 484  |

|                |         | 25.3.3.2    | FlexNVM Partition Code                              | 485  |

|                | 25.3.4  | Register I  | Descriptions                                        | 486  |

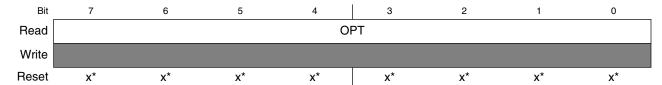

|                |         | 25.34.1     | Flash Option Register (FTFL_FOPT)                   | 487  |

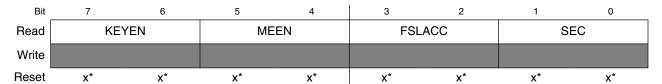

|                |         | 25.34.2     | Flash Security Register (FTFL_FSEC)                 | 488  |

|                |         | 25.34.3     | Flash Configuration Register (FTFL_FCNFG)           | 489  |

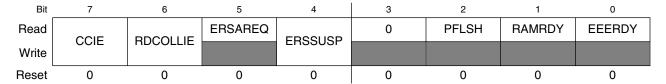

|                |         | 25.34.4     | Flash Status Register (FTFL_FSTAT)                  | 491  |

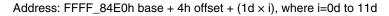

|                |         | 25.34.5     | Flash Common Command Object Registers (FTFL_FCCOBn) | 493  |

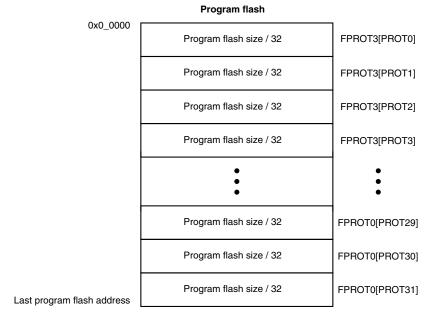

|                |         | 25.34.6     | Program Flash Protection Registers (FTFL_FPROTn)    | 494  |

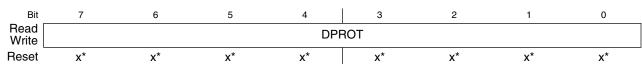

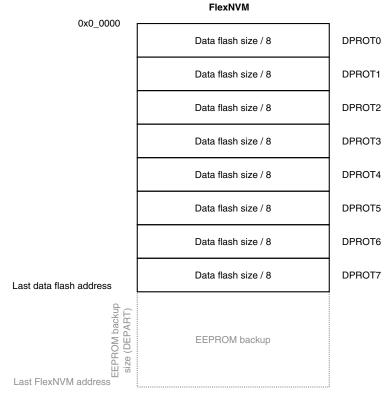

|                |         | 25.34.7     | Data Flash Protection Register (FTFL_FDPROT)        | 495  |

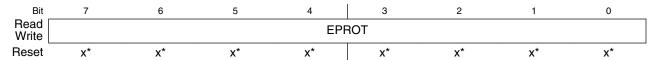

|                |         | 25.34.8     | EEPROM Protection Register (FTFL_FEPROT)            | 496  |

| 25.4           | Functio | nal Descrip | tion                                                | 497  |

|                | 25.4.1  | Flash Prot  | tection                                             | 497  |

|                | 25.4.2  | FlexNVM     | I Description                                       | 499  |

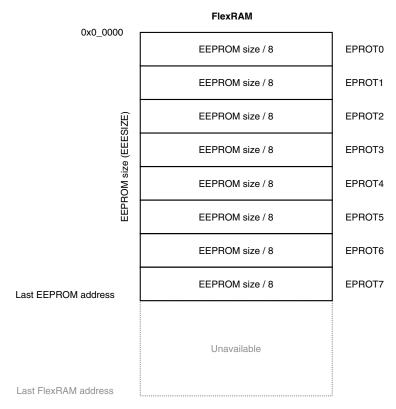

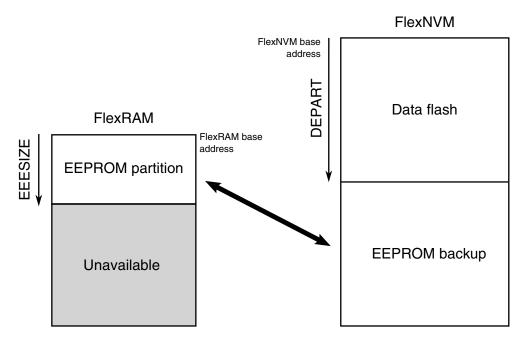

|                |         | 25.4.2.1    | FlexNVM Block Partitioning for FlexRAM              | 499  |

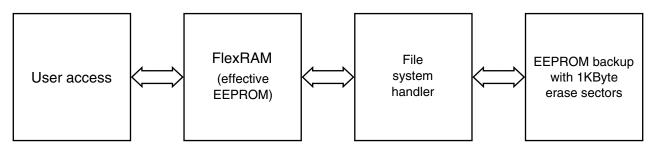

|                |         | 25.4.2.2    | EEPROM User Perspective                             | 500  |

|                |         | 25.4.2.3    | EEPROM Implementation Overview.                     | 501  |

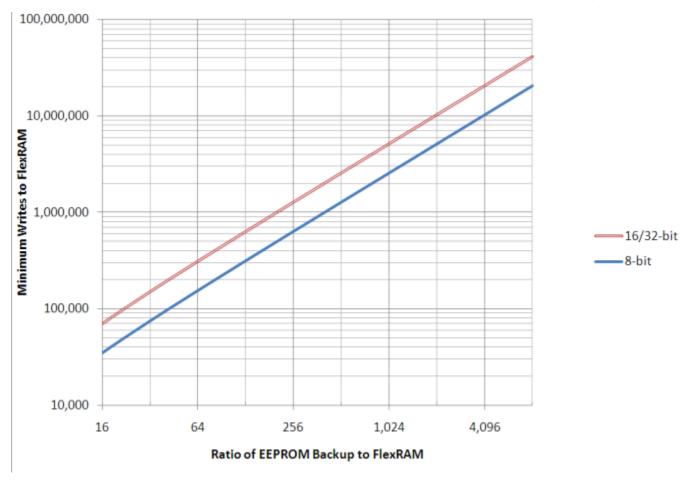

|                |         | 25.4.2.4    | Write endurance to FlexRAM for EEPROM               | 502  |

|                | 25.4.3  | Interrupts  |                                                     | 503  |

|                | 25.4.4  | Flash Ope   | eration in Low-Power Modes                          | 504  |

|                |         | 25.4.4.1    | Wait Mode                                           | 504  |

|                |         | 25.4.4.2    | Stop Mode                                           | 504  |

|                | 25.4.5  | Functiona   | ll Modes of Operation                               | 504  |

|                | 25.4.6  | Flash Rea   | ds and Ignored Writes                               | 504  |

| ection | number         | litte                                    | Page |

|--------|----------------|------------------------------------------|------|

| 25.4   | 1.7 Read Whi   | ile Write (RWW)                          | 505  |

| 25.4   | 4.8 Flash Pro  | gram and Erase                           | 505  |

| 25.4   | 4.9 Flash Cor  | mmand Operations                         | 505  |

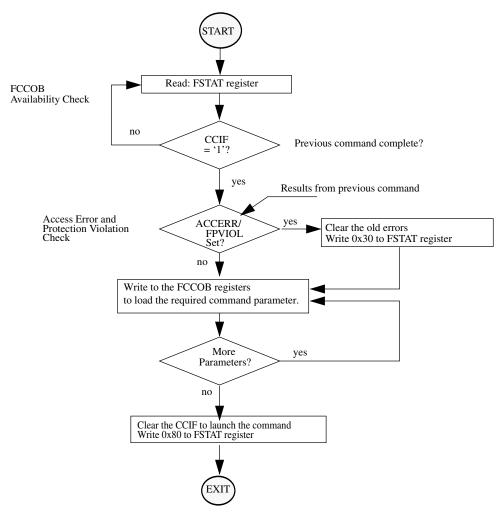

|        | 25.4.9.1       | Command Write Sequence                   | 506  |

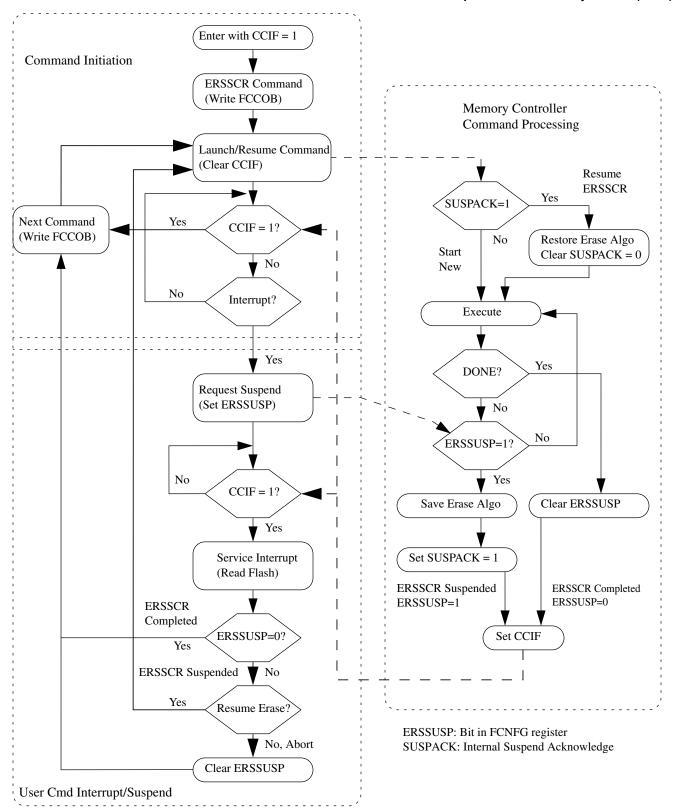

|        | 25.4.9.2       | Flash Commands                           | 508  |

|        | 25.4.9.3       | Flash Commands by Mode                   | 511  |

|        | 25.4.9.4       | Allowed Simultaneous Flash Operations    | 511  |

| 25.4   | 4.10 Margin R  | lead Commands                            | 512  |

| 25.4   | 4.11 Flash Cor | mmand Description                        | 513  |

|        | 25.4.11.1      | Read 1s Block Command                    | 514  |

|        | 25.4.11.2      | Read 1s Section Command                  | 515  |

|        | 25.4.11.3      | Program Check Command                    | 516  |

|        | 25.4.11.4      | Read Resource Command                    | 517  |

|        | 25.4.11.5      | Program Longword Command                 | 518  |

|        | 25.4.11.6      | Erase Flash Block Command                | 519  |

|        | 25.4.11.7      | Erase Flash Sector Command               | 520  |

|        | 25.4.11.8      | Program Section Command                  | 523  |

|        | 25.4.11.9      | Read 1s All Blocks Command               | 525  |

|        | 25.4.11.10     | 0 Read Once Command                      | 527  |

|        | 25.4.11.1      | 1 Program Once Command                   | 527  |

|        | 25.4.11.12     | 2 Erase All Blocks Command               | 528  |

|        | 25.4.11.13     | 3 Verify Backdoor Access Key Command     | 529  |

|        | 25.4.11.14     | 4 Program Partition Command              | 531  |

|        | 25.4.11.1:     | 5 Set FlexRAM Function Command           | 533  |

| 25.4   | 4.12 Security  |                                          | 534  |

|        | 25.4.12.1      | Flash Memory Access by Mode and Security | 535  |

|        | 25.4.12.2      | Changing the Security State              | 535  |

| 25.4   | 4.13 Reset Seq | quence                                   | 536  |

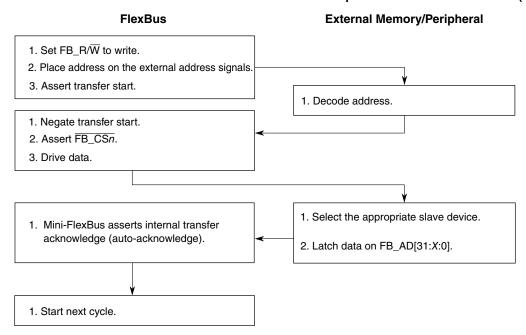

# Chapter 26 External Bus Interface (Mini-FlexBus)

| 26.1 | Introduction |                                                   |     |  |  |

|------|--------------|---------------------------------------------------|-----|--|--|

|      | 26.1.1       | Definition                                        | 539 |  |  |

|      | 26.1.2       | Features                                          | 540 |  |  |

| 26.2 | Signal d     | escriptions                                       | 540 |  |  |

| 26.3 | Memory       | Map/Register Definition                           | 541 |  |  |

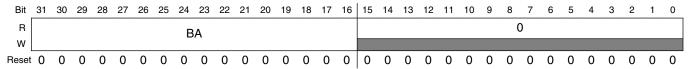

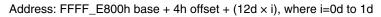

|      | 26.3.1       | Chip Select Address Register (FB_CSARn)           | 542 |  |  |

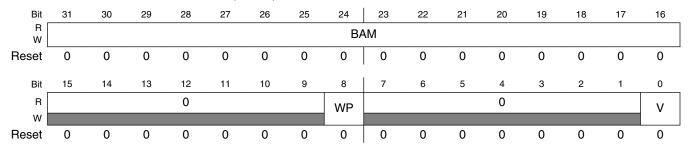

|      | 26.3.2       | Chip Select Mask Register (FB_CSMRn)              | 543 |  |  |

|      | 26.3.3       | Chip Select Control Register (FB_CSCRn)           | 544 |  |  |

| 26.4 | Function     | nal description                                   | 546 |  |  |

|      | 26.4.1       | Modes of operation                                | 546 |  |  |

|      | 26.4.2       | Address comparison                                | 546 |  |  |

|      | 26.4.3       | Address driven on address bus                     |     |  |  |

|      | 26.4.4       | Connecting address/data lines                     |     |  |  |

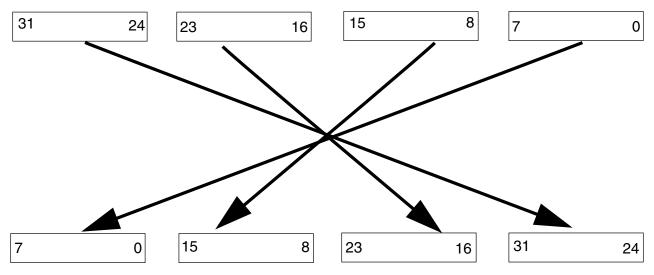

|      | 26.4.5       | Bit ordering.                                     |     |  |  |

|      | 26.4.6       | Data transfer signals                             | 547 |  |  |

|      | 26.4.7       | Signal transitions.                               | 547 |  |  |

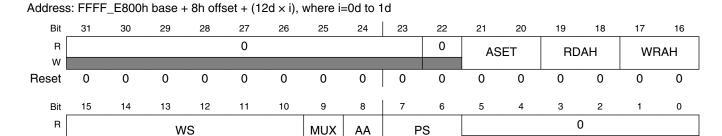

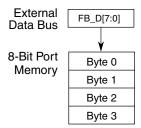

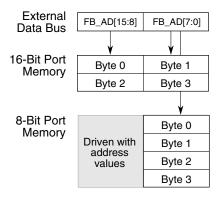

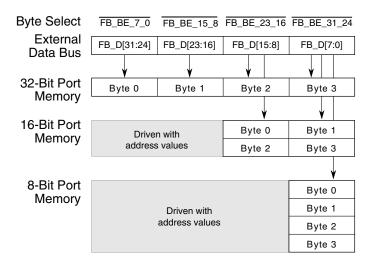

|      | 26.4.8       | Data-byte alignment and physical connections      | 548 |  |  |

|      | 26.4.9       | Address/data bus multiplexing                     | 549 |  |  |

|      |              | 26.4.9.1 Mini-FlexBus multiplexed operating modes | 549 |  |  |

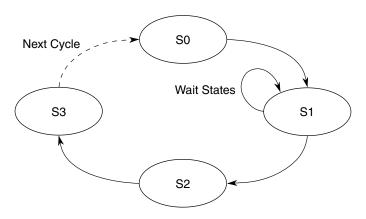

|      | 26.4.10      | Data transfer states                              | 550 |  |  |

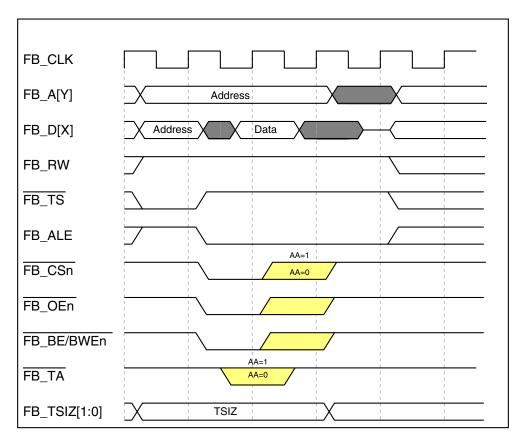

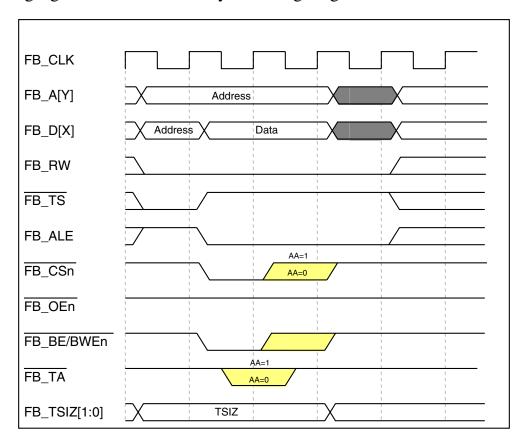

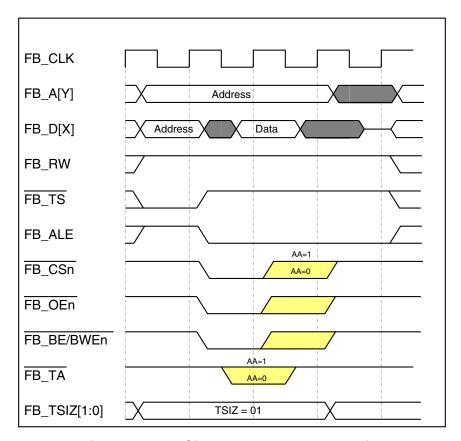

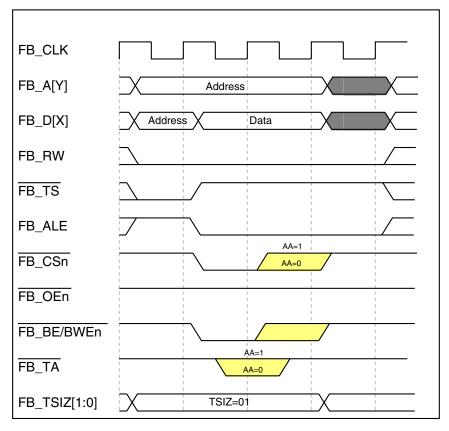

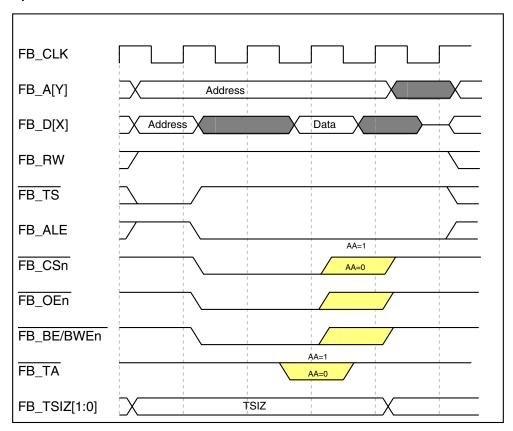

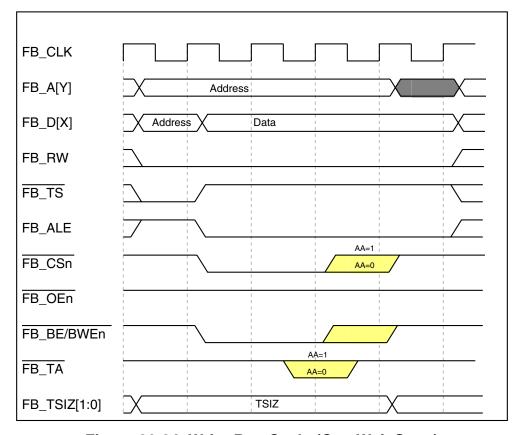

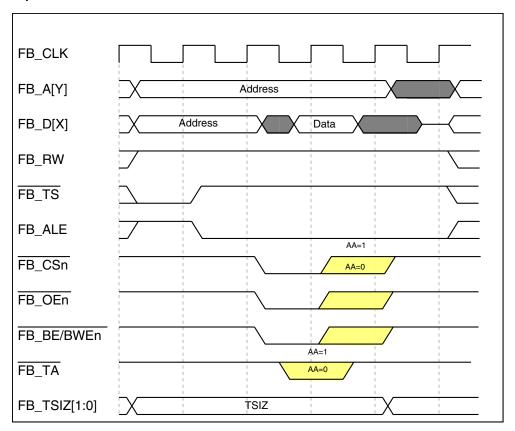

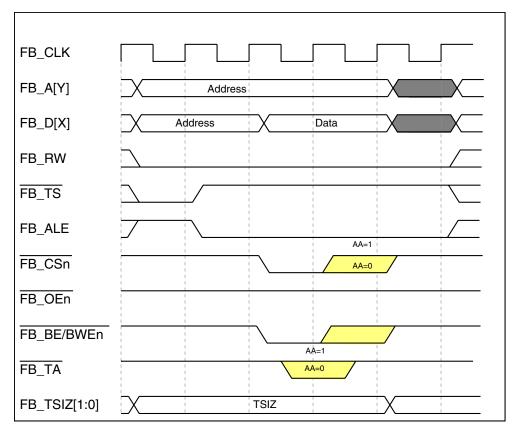

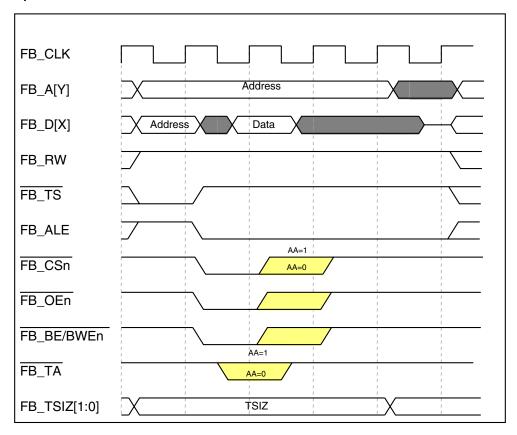

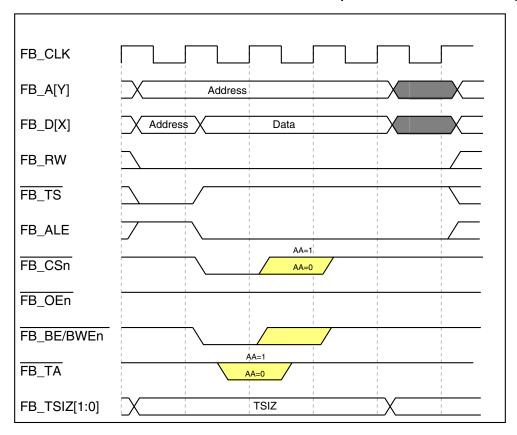

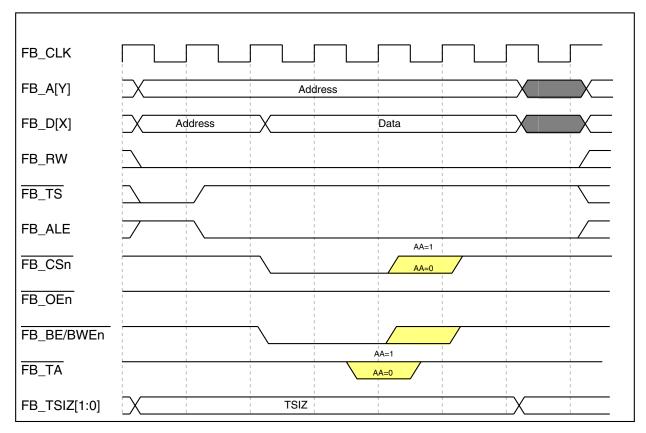

|      | 26.4.11      | Mini-FlexBus Timing Examples.                     | 550 |  |  |

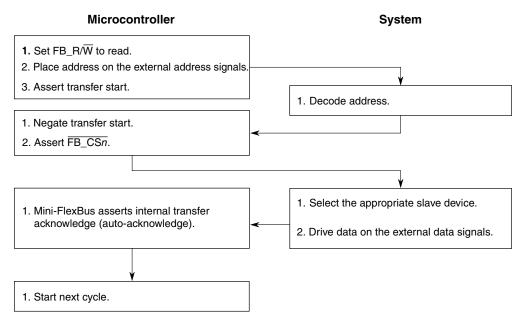

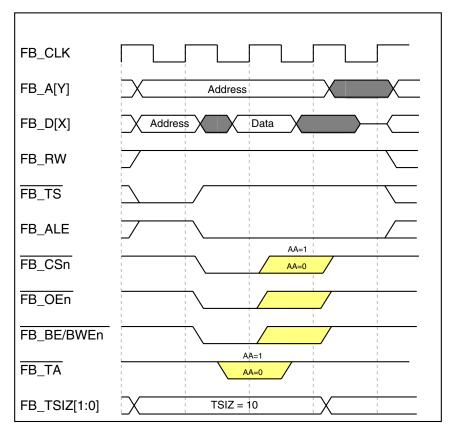

|      |              | 26.4.11.1 Basic Read Bus Cycle                    | 551 |  |  |

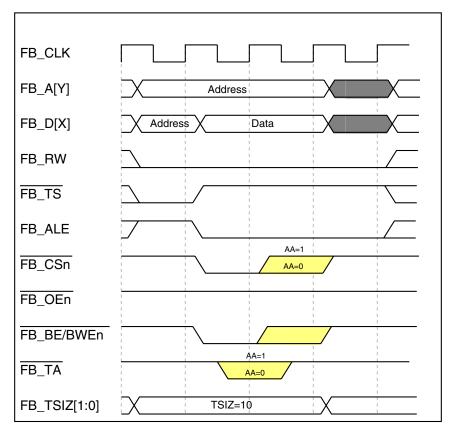

|      |              | 26.4.11.2 Basic Write Bus Cycle                   | 552 |  |  |

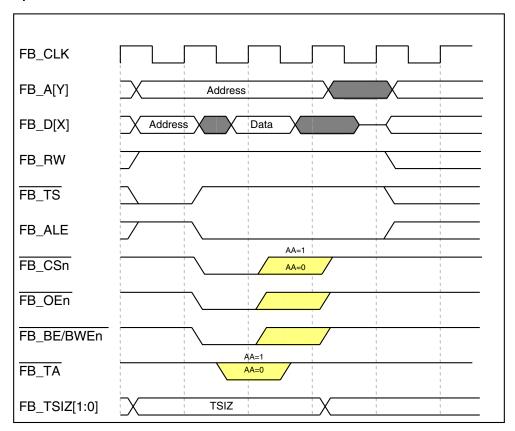

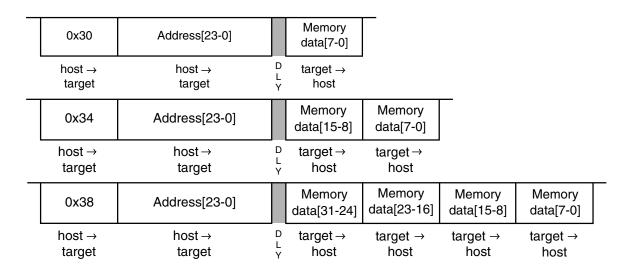

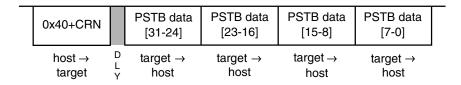

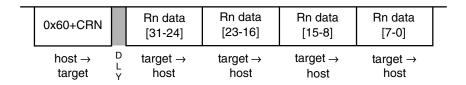

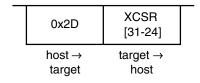

|      |              | 26.4.11.3 Bus Cycle Sizing                        | 553 |  |  |

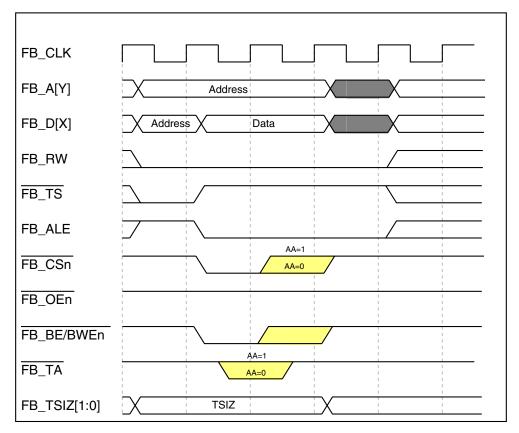

|      |              | 26.4.11.4 Timing Variations                       | 557 |  |  |

|      | 26.4.12      | Bus errors                                        | 566 |  |  |

| Section number |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Title                                                                                                                                                                                                                                                                                                                                                                                    | Page                                   |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Initializ      | ation/Applic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | cation Information                                                                                                                                                                                                                                                                                                                                                                       | 566                                    |

| 26.5.1         | Initializing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | g a chip-select                                                                                                                                                                                                                                                                                                                                                                          | 567                                    |